Université de Versailles Saint-Quentin-en-Yvelines

### Généralisation de l'Analyse de Performance Décrémentale vers l'Analyse Différentielle

### Generalization of the Decremental Performance Analysis to Differential Analysis

## **THÈSE**

pour l'obtention du

# Doctorat de l'Université de Versailles Saint-Quentin-en-Yvelines (spécialité informatique)

par

#### Zakaria Bendifallah

Directeur de thèse : William Jalby - Professeur, Université de Versailles,

France

Président : Lee W.Baugh - Ingénieur, Google, Seattle, USA

Rapporteurs: Albert Cohen - Directeur de recherche, INRIA, France

Michel Krajecki - Professeur, Université de Reims, France

Examinateurs: Edouard Audit - Directeur, Maison de la Simulation, France

Andry Razafinjatovo - Ingénieur, Bull, France

Jean-Thomas Acquaviva - Ingénieur, DataDirect Networks, France

## Remerciements

$\grave{A}$  mes parents et mes soeurs

#### Résumé:

Une des étapes les plus cruciales dans le processus d'analyse des performances d'une application est la détection des goulets d'étranglement. Un goulet étant tout évènement qui contribue  $\tilde{A}$  l'allongement temps d'exécution, la détection de ses causes est importante pour les développeurs d'applications afin de comprendre les défauts de conception et de génération de code.

Cependant, la détection de goulets devient un art difficile. Dans le passé, des techniques qui reposaient sur le comptage du nombre d'évènements, arrivaient facilement à trouver les goulets. Maintenant, la complexité accrue des micro-architectures modernes et l'introduction de plusieurs niveaux de parallélisme ont rendu ces techniques beaucoup moins efficaces. Par conséquent, il y a un réel besoin de réflexion sur de nouvelles approches.

Notre travail porte sur le développement d'outils d'évaluation de performance des boucles de calculs issues d'applications scientifiques. Nous travaillons sur DECAN, un outil d'analyse de performance qui présente une approche intéressante et prometteuse appelée l'Analyse Décrémentale. DECAN repose sur l'idée d'effectuer des changements contrôlés sur les boucles du programme et de comparer la version obtenue (appelée variante) avec la version originale, permettant ainsi de détecter la présence ou pas de goulets d'étranglement.

Tout d'abord, nous avons enrichi DECAN avec de nouvelles variantes, que nous avons conçues, testées et validées. Ces variantes sont, par la suite, intégrées dans une analyse de performance poussée appelée l'Analyse Différentielle. Nous avons intégré l'outil et l'analyse dans une méthodologie d'analyse de performance plus globale appelée PAMDA.

Nous décrirons aussi les différents apports à l'outil DECAN. Sont particulièrement détaillées les techniques de préservation des structures de contrôle du programme, ainsi que l'ajout du support pour les programmes parallèles.

Finalement, nous effectuons une étude statistique qui permet de vérifier la possibilité d'utiliser des compteurs d'évènements, autres que le temps d'exécution, comme métriques de comparaison entre les variantes DECAN.

Mots clés : analyse de performances, réécriture binaire, analyse dynamique, analyse statique du code, optimization de code, parallélisme, accès mémoire, compteurs matérielle.

#### Abstract:

A crucial step in the process of application performance analysis is the accurate detection of program bottlenecks. A bottleneck is any event which contributes to extend the execution time. Determining their cause is important for application developpers as it enable them to detect code design and generation flaws.

Bottleneck detection is becoming a difficult art. Techniques such as event counts, which succeeded to find bottlenecks easily in the past, became less efficient because of the increasing complexity of modern micro-processors, and because of the introduction of parallelism at several levels. Consequently, a real need for new analysis approaches is present in order to face these challenges.

Our work focuses on performance analysis and bottleneck detection of compute intensive loops in scientific applications. We work on DECAN, a performance analysis and bottleneck detection tool, which offers an interesting and promising approach called Decremental Analysis. The tool, which operates at binary level, is based on the idea of performing controlled modifications on the instructions of a loop, and comparing the new version (called variant) to the original one. The goal is to assess the cost of specific events, and thus the existence or not of bottlenecks.

Our first contribution, consists of extending DECAN with new variants that we designed, tested and validated. Based on these variants, we developed analysis methods which we used to characterize hot loops and find their bottlenecks. We later, integrated the tool into a performance analysis methodology (PAMDA) which coordinates several analysis tools in order to achieve a more efficient application performance analysis.

Second, we introduce several improvements on the DECAN tool. Techniques developed to preserve the control flow of the modified programs, allowed to use the tool on real applications instead of extracted kernels. Support for parallel programs (thread and process based) was also added.

Finally, our tool primarily relying on execution time as the main concern for its analysis process, we study the opportunity of also using other hardware generated events, through a study of their stability, precision and overhead.

**Keywords:** performance analysis, binary rewriting, dynamic code analysis, static code analysis, code optimization, parallelism, memory accesses, hardware counters.

## Contents

| T | Inti                       | coduction                                                |

|---|----------------------------|----------------------------------------------------------|

| 2 | Bac                        | ekground on Micro-Processor Architecture                 |

|   | 2.1                        | Uni-core Design details                                  |

|   |                            | 2.1.1 Pipeline                                           |

|   |                            | 2.1.2 Multiple Issue Processors                          |

|   |                            | 2.1.3 Vector Extensions                                  |

|   |                            | 2.1.4 Out-Of-Order Execution                             |

|   |                            | 2.1.5 Caches                                             |

|   | 2.2                        | Multi-core Designs                                       |

|   |                            | 2.2.1 Multiple Cores[92]                                 |

|   |                            | 2.2.2 Cache Organization[21]                             |

|   |                            | 2.2.3 Shared Memory Support[89]                          |

|   | 2.3                        | GPUs and Many-Core Designs                               |

|   |                            | 2.3.1 Graphical Processing Units (GPUs)                  |

|   |                            | 2.3.2 Many-cores                                         |

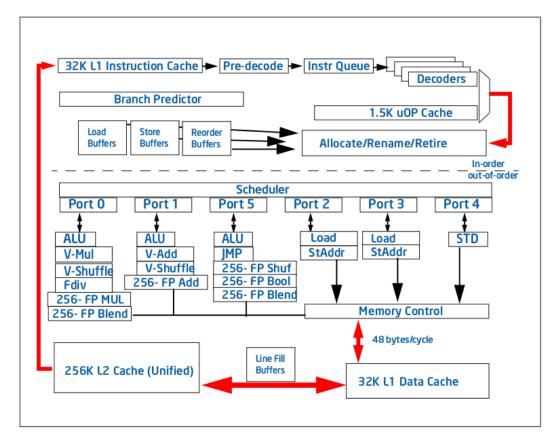

|   | 2.4                        | Design Example: Intel Sandy-Bridge Architecture          |

|   | 2.5                        | Summary                                                  |

|   | 2.0                        | Summary                                                  |

| 3 | $\mathbf{Ap}_{\mathbf{I}}$ | plication Performance Analysis                           |

|   | 3.1                        | Performance Life-cycle                                   |

|   | 3.2                        | Performance Evaluation                                   |

|   |                            | 3.2.1 Techniques                                         |

|   |                            | 3.2.2 Performance Pathologies and detection methods      |

|   | 3.3                        | Performance Evaluation Tools                             |

|   | 3.4                        | Discussion                                               |

|   | 3.5                        | summary                                                  |

| 4 | Dif                        | ferential Analysis                                       |

| 4 | 4.1                        | Introduction                                             |

|   | 4.2                        | Motivating Example                                       |

|   | 4.3                        | DECAN: Practical Design                                  |

|   | 4.0                        | 4.3.1 Principle                                          |

|   |                            |                                                          |

|   |                            |                                                          |

|   |                            |                                                          |

|   |                            | 4.3.4 Semantic Alteration                                |

|   |                            | 4.3.5 Performance Monitoring                             |

|   |                            | 4.3.6 Parallel Codes                                     |

|   | 4.4                        | DECAN Variants Design                                    |

|   |                            | 4.4.1 Instruction Subsets                                |

|   |                            | 4.4.2 Transformations                                    |

|   |                            | 4.4.3 Decan Variants                                     |

|   | 4.5                        | Differential Analysis: Main Analysis Methods and Metrics |

|   |                            | 4.5.1 Observable Events                                  |

|   |                            | 4.5.2 Saturation                                         |

vi Contents

|   |      | 4.5.3   | LS/FP Analysis                                             | 40 |

|---|------|---------|------------------------------------------------------------|----|

|   |      | 4.5.4   | Data Location and Return On Investment                     | 42 |

|   |      | 4.5.5   | Expensive Instructions                                     | 43 |

|   |      | 4.5.6   | Array Cost Analysis                                        | 44 |

|   | 4.6  | Case S  | Studies                                                    |    |

|   |      | 4.6.1   | Application Characterization and Analysis: RTM application | 47 |

|   |      | 4.6.2   | ACA: EUFLUXm Application                                   | 49 |

|   |      | 4.6.3   | L1 Load Bandwidth Evaluation                               |    |

|   | 4.7  | Summ    | nary                                                       | 52 |

| 5 | PAN  | лdа: l  | Performance Assessment using Maqao toolset and Di          | f- |

|   | fere | ntial A | Analysis                                                   | 53 |

|   | 5.1  | Introd  | luction                                                    |    |

|   | 5.2  |         | ating Example                                              |    |

|   | 5.3  | Ingred  | lients: Main Tool Set Components                           | 57 |

|   |      | 5.3.1   | MicroTools: Microbenchmarking the Architecture             | 58 |

|   |      | 5.3.2   | CQA: Code Quality Analyzer                                 | 58 |

|   |      | 5.3.3   | Decan: Differential Analysis                               | 58 |

|   |      | 5.3.4   | Mtl: Memory Tracing Library                                | 59 |

|   | 5.4  | Recipe  | e: Pamda Tool Chain                                        | 60 |

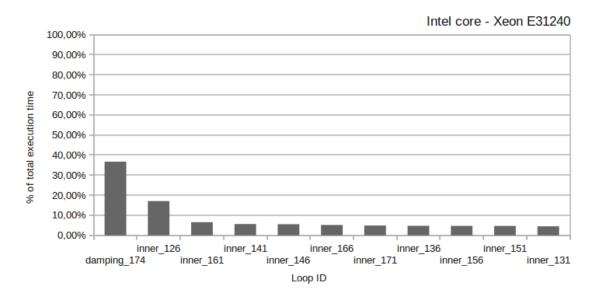

|   |      | 5.4.1   | Hotspot identification                                     | 60 |

|   |      | 5.4.2   | Performance overview                                       | 60 |

|   |      | 5.4.3   | Loop structure check                                       | 61 |

|   |      | 5.4.4   | CPU evaluation                                             | 61 |

|   |      | 5.4.5   | Bandwidth measurement                                      | 62 |

|   |      | 5.4.6   | Memory evaluation                                          | 63 |

|   |      | 5.4.7   | OpenMP evaluation                                          | 63 |

|   | 5.5  | Exper   | imental results                                            | 63 |

|   |      | 5.5.1   | PN                                                         | 64 |

|   |      | 5.5.2   | RTM                                                        | 65 |

|   | 5.6  | Relate  | ed Work                                                    | 67 |

|   | 5.7  | Summ    | ary                                                        | 68 |

| 6 |      |         | Assembly Level Re-writing Challenges and Limitations       | 69 |

|   | 6.1  |         | luction                                                    |    |

|   | 6.2  |         | N Technical Design                                         |    |

|   |      | 6.2.1   | General Overview of the Maqao Framework                    |    |

|   |      | 6.2.2   | DECAN architecture                                         |    |

|   | 6.3  |         | ng with Control Flow issues in DECAN                       |    |

|   |      | 6.3.1   | Data Dependent Control Flow                                |    |

|   |      | 6.3.2   | In-vitro Mode                                              |    |

|   |      | 6.3.3   | In-vivo Mode                                               | 76 |

|   | 6.4  | Extens  | sions for Parallel Applications                            | 78 |

|   |      | 6.4.1   | Shared Memory Codes                                        |    |

|   |      | 6.4.2   | Distributed Memory Codes                                   |    |

|   | 6.5  |         | Alteration Side Effects and Workarounds                    |    |

|   |      | 6.5.1   | Code Layout Sensitivity                                    | 81 |

|   |      | 6.5.2   | Data Dependence Alteration                                 |    |

|   |      | 6.5.3   | Instructions with variable Latencies                       | 85 |

Contents

|    |       | 6.5.4 Instrumentation Side Effects                            | 86  |

|----|-------|---------------------------------------------------------------|-----|

|    |       | 6.5.5 Floating-point Exceptions                               | 86  |

|    |       | 6.5.6 Wrap-up: Side Effects Sources                           | 87  |

|    | 6.6   | Summary                                                       | 88  |

| 7  | Tacl  | kling Measurement Precision, Stability and Probe Intrusive-   |     |

|    | ness  |                                                               | 89  |

|    | 7.1   | Introduction                                                  | 89  |

|    | 7.2   | Events of Interest                                            | 90  |

|    | 7.3   | Experimental Methodology                                      | 90  |

|    | 7.4   | Measurement Stability                                         | 91  |

|    |       | 7.4.1 Estimation                                              | 92  |

|    | 7.5   | Measurement Precision                                         | 94  |

|    |       | 7.5.1 Small Regions                                           | 94  |

|    |       | 7.5.2 Probes Accuracy                                         | 96  |

|    | 7.6   | Probe Intrusiveness                                           | 99  |

|    |       | 7.6.1 Relationship Between Event Type and Probe Intrusiveness | 99  |

|    |       | 7.6.2 Reducing Probe Intrusiveness With DECAN                 | 100 |

|    |       | 7.6.3 Experimental Results                                    | 101 |

|    | 7.7   | Summary                                                       | 103 |

| 8  | Con   | clusions                                                      | 105 |

|    | 8.1   | Perspectives                                                  | 106 |

|    |       | 8.1.1 Tool Development                                        | 106 |

|    |       | 8.1.2 Research Topics                                         | 107 |

| Bi | bliog | raphy                                                         | 109 |

# List of Figures

| 2.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Vector operations on Intel architectures. The two technologies illustrated are SSE(Streaming SIMD Extensions) and Advanced Vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | Extensions (AVX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7  |

| 2.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 |

| 2.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12 |

| 2.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15 |

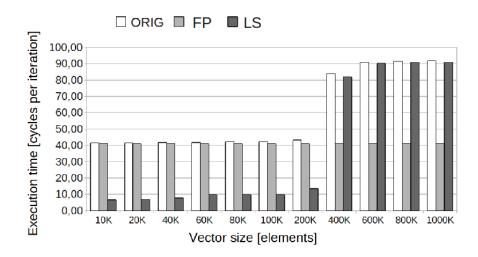

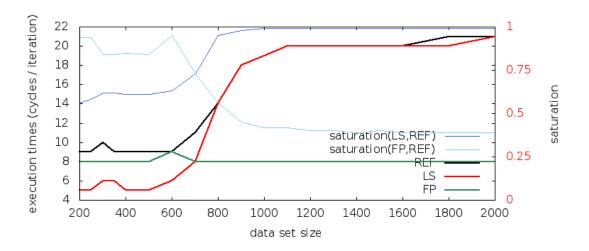

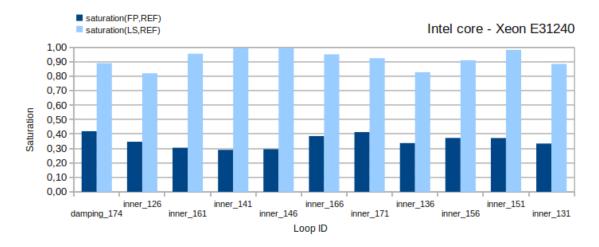

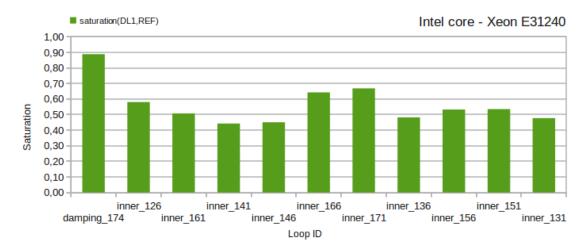

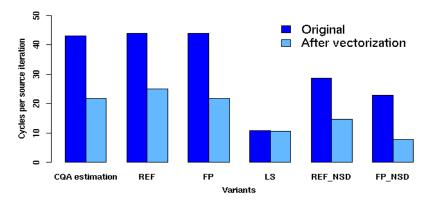

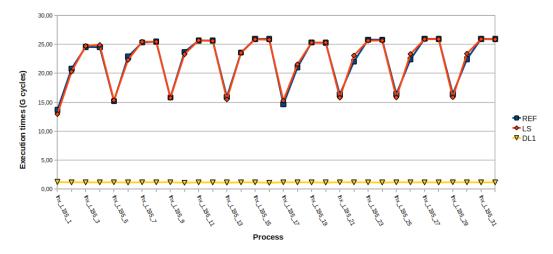

| 4.1  | Memory and Floating-point streams analysis with the variants LS and FP. The experiments are performed on 4 cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29 |

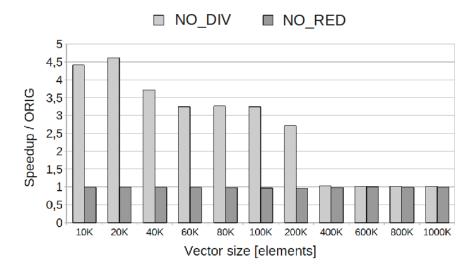

| 4.2  | Division and reduction impact analysis with the variants NO_DIV and NO_RED. The experiments are performed on 4 cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29 |

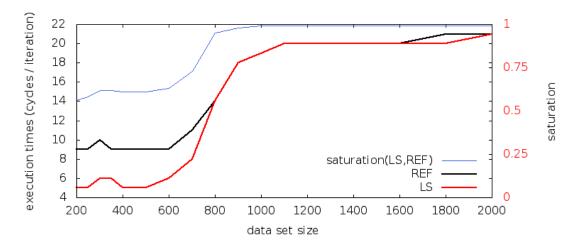

| 4.3  | Execution time and saturation curves for NR codelet mprove on different data sizes for a four cores execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40 |

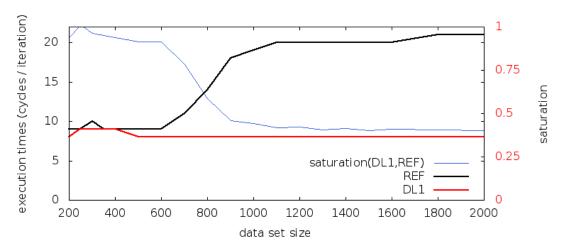

| 4.4  | Execution time and saturation curves for NR codelet mprove on different data sizes. Results are for a four cores execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12 |

| 4.5  | Execution time and saturation curves for NR codelet mprove on different data sizes for a four cores execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43 |

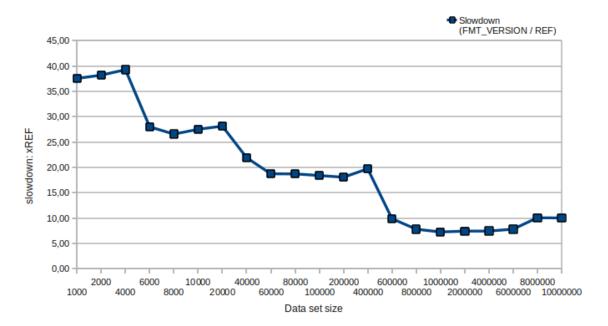

| 4.6  | Execution Slowdown of a version of the loop instrumented to perform FMT over its original version for BALAN_3 codelet on different data sizes. The four levels of slowdown correspond from left to right to                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | data being in L1, L2, L3 caches and RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17 |

| 4.7  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18 |

| 4.8  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48 |

| 4.9  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19 |

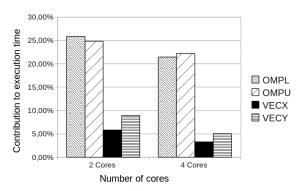

| 4.10 | The left figure illustrates the source code of the matrix-vector product in EUFLUXm. The right figure shows the individual contribution in the overall execution time of memory instructions targeting each array of the EUFLUXm routine. Results are presented for 2 and 4 cores 5                                                                                                                                                                                                                                                                                                                                                       | 50 |

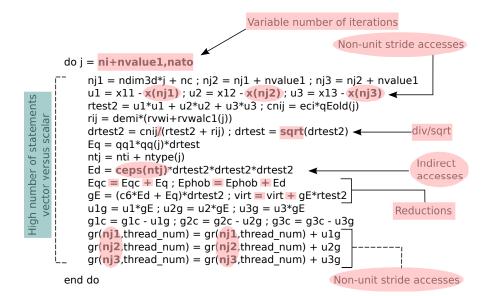

| 5.1  | A Fortran source code sample and its main performance pathologies highlighted in pink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56 |

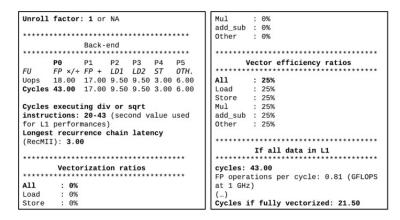

| 5.2  | Comparing static estimates obtained by CQA with dynamic measurements performed on different code variants generated by DECAN of both the original and the vectorized versions: <b>REF</b> is the reference binary loop (no binary modifications introduced by DECAN), <b>FP</b> (resp. <b>LS</b> ) is the DECAN binary loop variant in which all of the Load/Store (resp. FP) instructions have been suppressed, <b>REF_NSD</b> (resp. <b>FP_NSD</b> ) is the DECAN binary loop variant in which only FP sqrt and div instructions (resp. all of the Load/Store and FP sqrt/div instructions) have been suppressed. The y-axis represents | 56 |

| 5.3  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59 |

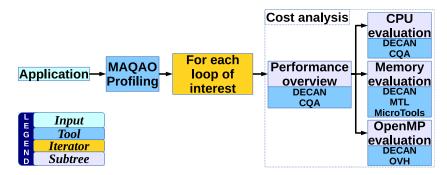

| 5.4  | Pampa overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30 |

List of Figures

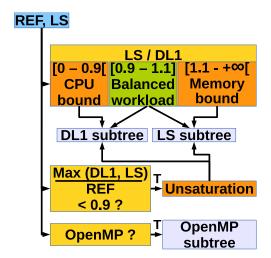

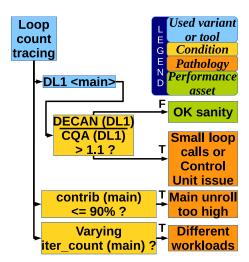

| 5.5      | Performance investigation overview. T means the condition is True, otherwise it is False (F)                                                                                                                                                                                        | 60 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.6      | Detecting structural issues.                                                                                                                                                                                                                                                        | 61 |

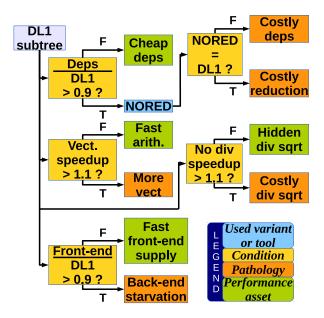

| 5.7      | DL1 subtree: CPU performance evaluation                                                                                                                                                                                                                                             | 62 |

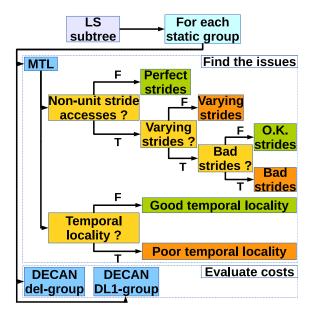

| 5.8      | LS subtree: Memory performance evaluation                                                                                                                                                                                                                                           | 63 |

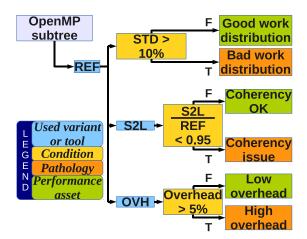

| 5.9      | OpenMP performance tree: STD represents the standard deviation                                                                                                                                                                                                                      | 00 |

| 5.9      | between threads while the OVH branch stands for OpenMP Overhead                                                                                                                                                                                                                     |    |

|          | evaluation                                                                                                                                                                                                                                                                          | 64 |

| 5 10     | Streams analysis on PN. The REF curve corresponds to performance                                                                                                                                                                                                                    | 01 |

| 5.10     | of the original code. The LS (resp. DL1) curve corresponds to the Decan variant where all FP instructions have been suppressed (resp.                                                                                                                                               | 64 |

| <b>-</b> | all data accesses are forced to come out of L1)                                                                                                                                                                                                                                     | 04 |

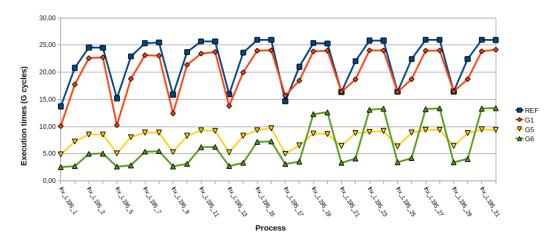

| 5.11     | Group cost analysis on PN. Each group curve corresponds to performance of the loop while the target group is deleted. The original code performance (REF) is used as a reference                                                                                                    | 65 |

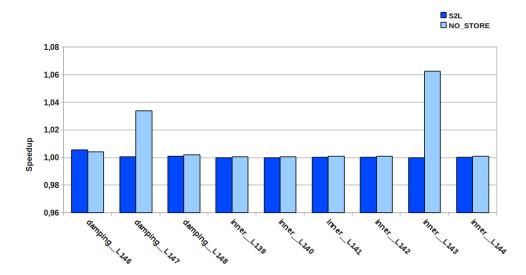

| 5.12     | Evaluation of the cost of cache coherence protocol. The S2L variants show similar performance as their corresponding reference versions. The NO STORE variants also show similar performances, except for                                                                           |    |

|          | two loops which present a relatively non negligible store cost                                                                                                                                                                                                                      | 66 |

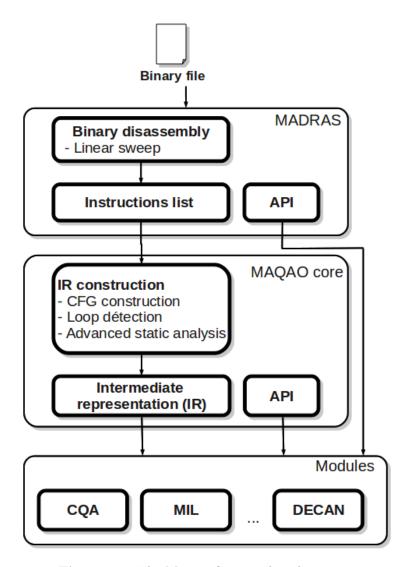

| 6.1      | The Maqao framework architecture                                                                                                                                                                                                                                                    | 70 |

| 6.2      | DECAN tool workflow                                                                                                                                                                                                                                                                 | 73 |

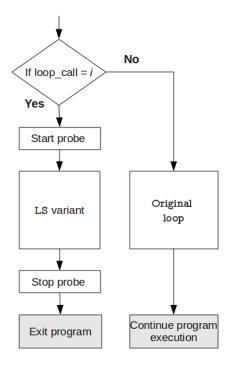

| 6.3      | Flowchart showing the logic of the code generated by DECAN for the instance mode. As long as the loop call i is not reached the original version of the loop is executed. Once the loop call is reached, the transformed version of the loop is activated. The program is ended     | 77 |

| 6.4      | at loop exit                                                                                                                                                                                                                                                                        | 77 |

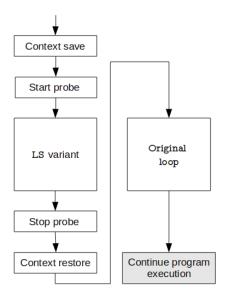

| 0.4      | recovery loop mode                                                                                                                                                                                                                                                                  | 78 |

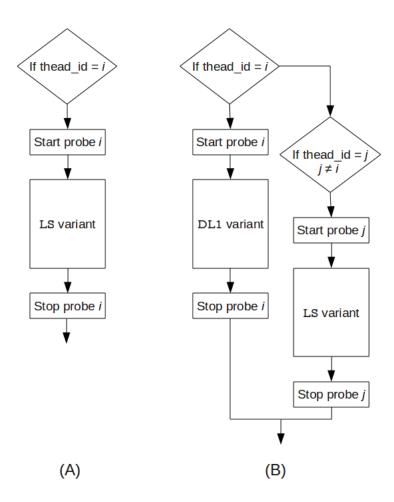

| 6.5      | Flowcharts showing the logic of the code generated by DECAN for the two openMP operatory modes. Flowchart (A) illustrates the case where all threads execute the same variant, and Flowchart (B) illustrates the case where different threads may executes different DECAN variants | 79 |

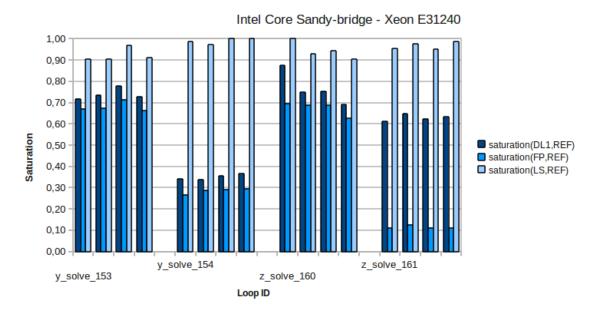

| 6.6      | DL1, FP and LS variants on the four of the hot loops of the BT bench-                                                                                                                                                                                                               | •• |

|          | mark                                                                                                                                                                                                                                                                                | 80 |

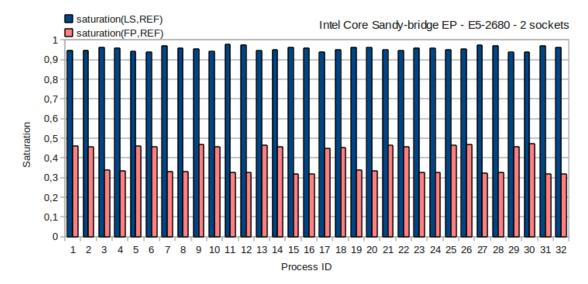

| 6.7      | Stream variants on 32 processes of the PN application                                                                                                                                                                                                                               | 81 |

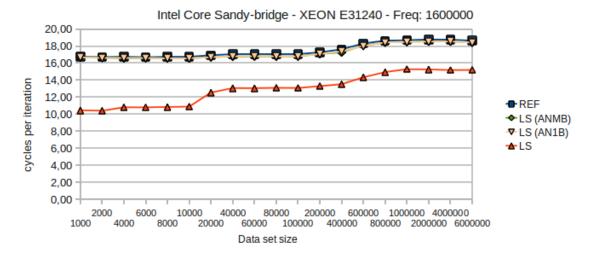

| 6.8      | Performance of the REF, LS(ANMB), LS(AN1B) and LS variants for the                                                                                                                                                                                                                  |    |

|          | NR codelet toeplz_4 on a low frequency execution                                                                                                                                                                                                                                    | 82 |

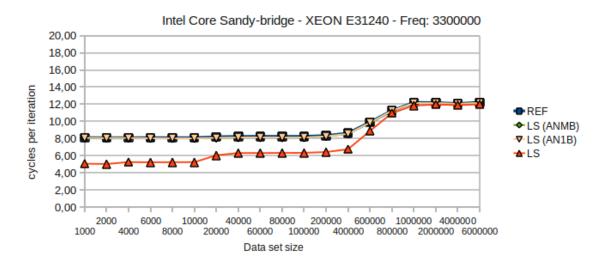

| 6.9      | Performance of the REF, LS(ANMB), LS(AN1B) and LS variants for the                                                                                                                                                                                                                  |    |

|          | NR codelet toeplz_4 on a high frequency execution                                                                                                                                                                                                                                   | 82 |

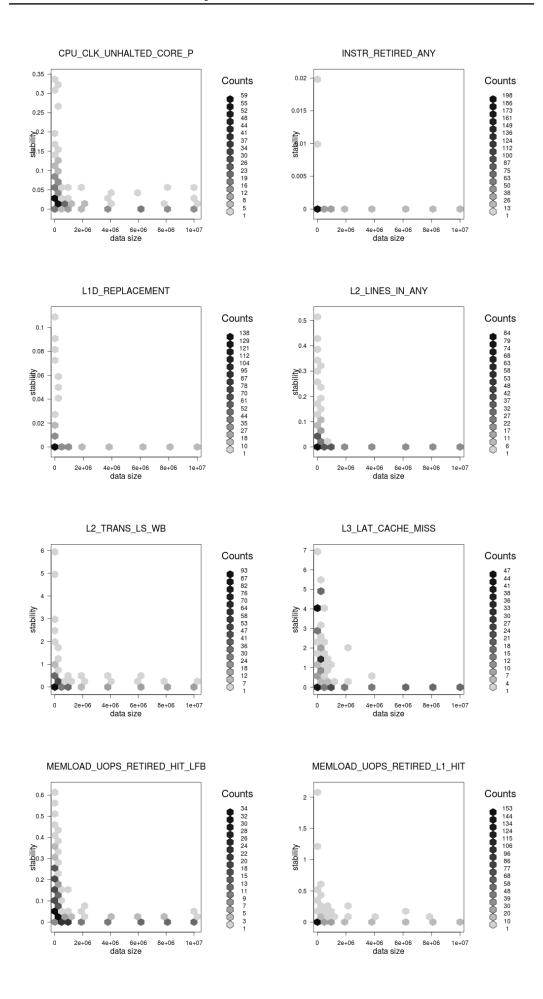

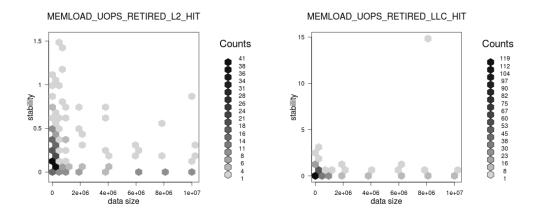

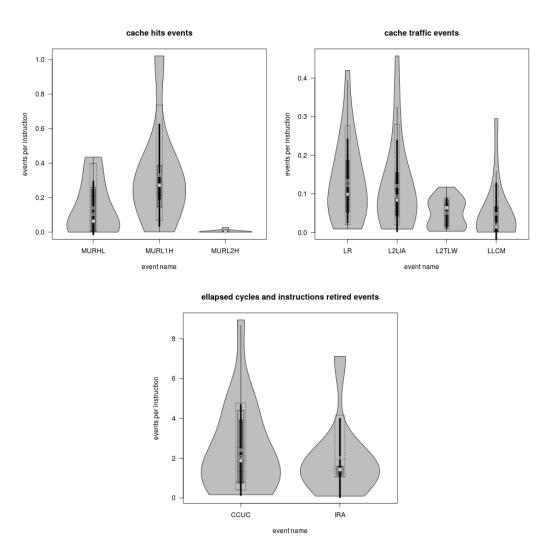

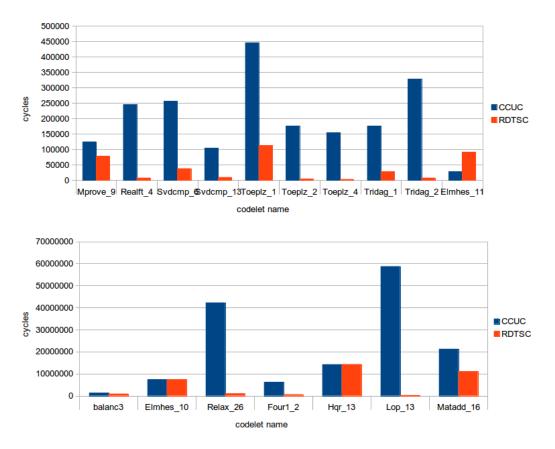

| 7.1      | For each event, the stability of all data size points for all the NR codelets of the test suite                                                                                                                                                                                     | 94 |

| 7.2      | hqr_12 codelet source and binary codes                                                                                                                                                                                                                                              | 95 |

| 7.3      | Evolution of the number of measured L1D_REPLACEMENT events per iteration following data size for balanc codelet                                                                                                                                                                     | 96 |

List of Figures xi

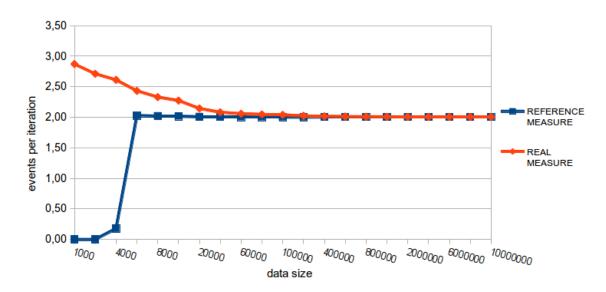

| 7.4 | Evolution     | of         | the                 | number        | of           | measured             |     |

|-----|---------------|------------|---------------------|---------------|--------------|----------------------|-----|

|     | MEMLOAD_UOF   | S_RETIR    | ED_L1_HIT           | events p      | er iteration | n following          |     |

|     | data size for | balanc c   | odelet              |               |              |                      | 96  |

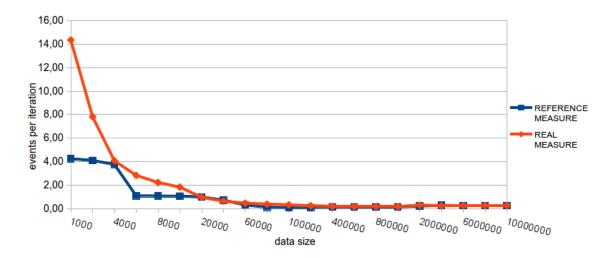

| 7.5 | For each eve  | nt, the di | stribution          | of the small  | est event co | unt starting         |     |

|     | from where t  | he real a  | nd referenc         | e measures    | match        |                      | 97  |

| 7.6 | Minimum cy    | cles coun  | t for which         | the real m    | easure mate  | ches the ref-        |     |

|     | erence meas   | ure for h  | eavy meas           | urement me    | ethod that   | accesses the         |     |

|     | CPU_CLK_      | UNHAL      | TED_COF             | E counter (   | (CCUC) an    | d light mea-         |     |

|     | surement me   | thod using | ng <b>rdtsc</b> . F | Results are s | hown for 17  | ${\rm NR}$ codelets. | 98  |

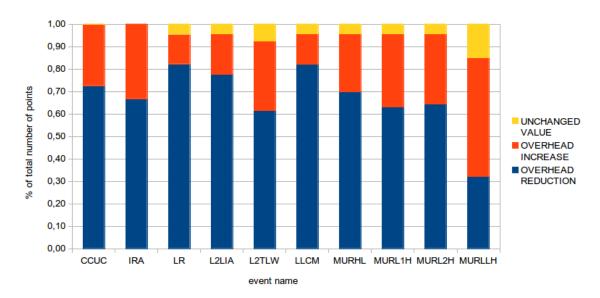

| 7.7 | Average erro  | r reducti  | on and err          | or increase   | after the su | btraction of         |     |

|     | events genera | ated by tl | ne probes           |               |              |                      | 101 |

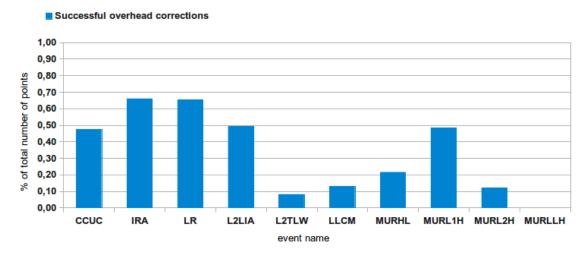

| 7.8 | Ratio of succ | essful ove | erhead corr         | ections (rela | tive error < | 0.05) among          |     |

|     | error reducti | ons (error | r increase c        | ases are not  | taken into   | account)             | 102 |

# List of Algorithms

| 1 | Code example                       | 28 |

|---|------------------------------------|----|

| 2 | LS/FP_analysis                     | 41 |

| 3 | Polaris (MD) loop 2937 source code | 51 |

| 4 | Reference measures                 | 91 |

| 5 | Real measures                      | 91 |

## List of Tables

| 3.1        | A few typical performance pathologies                                                                                                                                                                                                                                                  | 20       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.2        | Performance pathologies detection with static analysis techniques                                                                                                                                                                                                                      | 21       |

| 3.3        | Performance pathologies diagnosis with simulation techniques                                                                                                                                                                                                                           | 21       |

| 3.4        | Performance pathologies diagnosis with dynamic time profiling techniques                                                                                                                                                                                                               | 21       |

| 3.5        | Performance pathologies detection with hardware counters based techniques                                                                                                                                                                                                              | 22       |

| 4.1<br>4.2 | Assembly code of NR codelet SVDCMP_13 (SSE version) Advanced data-flow analysis tracks the symbolic values of registers. Based on registers value it is then possible to infer which instructions are targeting the same data structure. Such instructions are coalesced within groups | 33<br>35 |

| 4.3        | Operands order change for a store instruction (the instruction is transformed into a load)                                                                                                                                                                                             | 35       |

| 4.4        | Source operand deletion of a vector multiplication instruction (the instruction is transformed into a load)                                                                                                                                                                            | 36       |

| 4.5        | Vector multiplication instruction with a load operand transformed into a simple load instruction                                                                                                                                                                                       | 36       |

| 4.6        | Vector multiplication instruction with a load operand to which a prefetch instruction is added                                                                                                                                                                                         | 36       |

| 4.7        | Group detection results through both grouping static analysis and FMT runtime analysis                                                                                                                                                                                                 | 46       |

| 4.8        | Results of group reconstruction for EUFLUX application with the use of both static and dynamic (FMT) analyzes. The cost of each analysis in slowdown over original execution time is shown                                                                                             | 50       |

| 4.9        | Stream analysis for loop 2937 of POLARIS (MD)                                                                                                                                                                                                                                          | 51       |

| 4.10       | Effect of L1 cache bandwidth reduction on performance for loop 2937 of POLARIS (MD)                                                                                                                                                                                                    | 52       |

| 5.1        | A few typical performance pathologies                                                                                                                                                                                                                                                  | 55       |

| 5.2        | DECAN variants and transformations                                                                                                                                                                                                                                                     | 59       |

| 5.3        | Bytes per cycle for each memory level (Sandy Bridge E5-2680)                                                                                                                                                                                                                           | 62       |

| 5.4        | PN MTL results for the three most relevant instruction groups                                                                                                                                                                                                                          | 65       |

| 6.1        | Example of transformation which alters data dependency between instructions. The resulting instruction (V1) adds new dependencies                                                                                                                                                      |          |

| 6.2        | whereas (V2) preserves the original ones                                                                                                                                                                                                                                               | 83       |

|            | after transformation application                                                                                                                                                                                                                                                       | 84       |

| 6.3        | Comparison between the performance of REF variant and two versions of FP variant                                                                                                                                                                                                       | 01       |

| 6.4        | sions of FP variant                                                                                                                                                                                                                                                                    | 85<br>85 |

| 6.5        | Application of FP stream transformation on a code which contains a                                                                                                                                                                                                                     | 00       |

| 0.0        | division operation                                                                                                                                                                                                                                                                     | 86       |

xvi List of Tables

| 7.1 | List of hardware counters of interest, available in the Intel Sandy-    | -   |  |

|-----|-------------------------------------------------------------------------|-----|--|

|     | Bridge micro-architecture                                               | 90  |  |

| 7.2 | Expected values for the approximation of $l\_val$ following the type of |     |  |

|     | interaction between probe and loop events                               | 101 |  |

## Introduction

#### General context

How to complete the execution of a piece of code as fast as possible has always been a primary concern since the emergence of computing machines. This goal is tackled from several perspectives by different actors: hardware vendors seek to provide designs that can be efficiently exploited, programmers focus on algorithms more efficient in the exploitation of underlying architecture, compiler developers attempt to polish and optimize the written code and performance analysts try to find and fix performance issues affecting the final code. We subscribe to the later category and we also focus on HPC (high Performance Computing). HPC is characterized, on the software side, by major simulation programs for various domains(crash simulations, thermodynamics, molecular chemistry, etc), and on the hardware side, by the use of supercomputers, the biggest computing machines ever made.

The time to completion (time to finish the task or a program) is important in HPC. In his presentation,  $Tadashi\ Watanabe$ , Project Leader of Next-Generation Supercomputer R&D Center RIKEN and designer of the K supercomputer (the world's fastest supercomputer in 2011 and 4th fastest at the time of this writing) stated, two months after the  $Fukushima\ nuclear\ disaster$  in Japan, that the simulation of the tsunami wave took  $2\ hours$  with their fastest supercomputer at the time of the catastrophe, and that the same simulation only takes  $10\ minutes$  with the K supercomputer. Knowing that it took the tsunami approximatively  $50\ minutes$  to reach the nuclear power plant, he argued that the use of K would have given some time to start reacting to it.

However, recent years recorded new turns in processor evolution, uni-core processors were deprecated in favor of multi-core processors. Modern day supercomputers are clusters of processors, connected with either standard or dedicated communication networks, hence allowing thousands of processor cores to be exploited in parallel. This raised new challenges: energy consumption, for example, becomes a primary concern (the most powerful supercomputer at this time consumes near 17,808 KW [16]). Therefore, the energy consumed to complete the task becomes another goal which usually holds a trade-off relationship with the first one.

On the application side, several programming paradigms emerged. We thus find a widespread use of distributed memory models, notably with the use of the Message Passing Interface MPI [47]). They aim to exploit the parallelism offered by a high number of processors connected with a communication network. At node level, the use of shared memory models is common notably with technologies such as OpenMP [30] and Intel TBB [84]. Finally, at core level, we heavily rely on optimizing technology of compilers such as GCC [6] or ICC [10]. The objective is there to design a code generation scheme which allows to make the best use of the power offered by the hardware.

Providing powerful hardware is a valuable asset to achieve high performance. However, the aggregation of more computing power is not a solution in itself, due to the severe technical limitations such as communication latency and power consumption, as well as software limitations such as non-scaling algorithms. Additionally, compilers contribute to better performance, but by becoming too complex, they fail to find the optimal combination of optimizations. Performance analysis tools complete the cycle by giving feedback on the nature of performance bottlenecks and their locations.

#### Application Performance Analysis

Performance bottlenecks in HPC applications can be located at various levels. In a typical parallel application, they are generally ordered according to the granularity at which they occur: i) inter-node bottlenecks are at the highest granularity, they mainly concern communications between different processors, load balancing, synchronization, ii) intra-node bottlenecks are in a midst granularity and cover all intra-node interactions such as load balancing and data sharing between threads, iii) core bottlenecks are found at the lowest granularity and cover the good exploitation of hardware (vectorization, data locality, etc).

Each level of granularity has its own set of analysis techniques. For inter-node bottlenecks, the analysis is in general done through source code instrumentation. This does not affect the normal behaviour, the difficulties mainly being to handle the volume of collected data. As far as intra-node and core issues are concerned, the focus is put on fine grain bottlenecks. They are the direct effects of interaction between the code and the underlying architecture. Hardware related bottlenecks are very sensitive. A simple probe which monitors cache effects in the L1, can generate memory references and thus bias the result. Hardware vendors included in their designs what is known as performance monitoring units (PMUs), a set of hardware devices which monitor several micro-architectural actions (cache hits and misses, branch mis-predictions, number of instructions dispatched in each execution port). These made analysis tools less intrusive. However, they present some disadvantages too. The counters differ in their semantics from architecture to architecture and are not well documented. But most importantly, in the majority of cases, they only assess quantitive date, no qualitative such as the weight in terms of performance issues. They answer the question: "how often a particular event occured but give no information on how it affected performance". The number of occurrences is an interesting metric to characterize code fragments, but it fails to determine the impact of an event in a context where events may occur in parallel (the impact of an event can be partially or completely masked), which is the case in modern architectures (e.g. out-of-order execution and multi-threading).

Analysis methods are diverse too, in the previous paragraph we supposed that the analyses are performed on the program at runtime, the set of techniques based on this approach are gathered under the *measurement* category. It is also the category to which our work subscribes. The other two notable categories include *simulation* and *modeling*.

#### Contributions

Our work also includes measurement techniques. Traditional measurement and

instrumentation techniques rely on pure observation of the events. We believe that, at such small scale, it is difficult for a performance tool, given the complexity of modern architectures, to associate a weight (or cost) to a particular event (that could be a bottleneck). Our work starts from the base idea of event idealization, where a version of the code is created in which the event (e.g. memory reference) is idealized (suppressed), the performance change between the modified and original versions of the code indicates the impact of the event. The idea was first introduced with a tool called DECAN [57]. We propose to continue the development of the concept further to target more performance issues and broaden its use beyond application performance analysis.

With our research we make the following contributions:

New bottleneck identification techniques: we conceived, tested and validated new Decan variants that enabled us to identify performance bottlenecks. We also, redefined the concepts of the tool in a more abstract way in order to use them more easily on other architectures.

Moving from In-Vitro to In-Vivo mode: the previous version of the tool operated on extracted fragments of code (in-vitro mode). We developed techniques to use the tool at runtime directly on the loops of real industrial applications (in-vivo mode).

**Performance assessment methodology:** we use the flexibility of the technique and its characterization capabilities to make it play a central role in a methodology, aiming at coordinating several analysis tools and making them collaborate in bottleneck investigation. There is no need for a heavy tool when a lighter one can be used to investigate an issue.

Tackling measurement issues: we demonstrate that Differential Analysis can be applied to metrics other than time. To achieve that, we study how accurate and reliable hardware counters can be.

#### Outline

This dissertation is organized as follows:

- Chapter 2 discusses background and related work in the field. We review the important micro-architectural components in a modern micro-processor.

- Chapter 3 provides material for bottleneck detection by outlining well-known intra-node performance pathologies as well as the common diagnosis techniques.

- In Chapter 4 we introduce the building blocks that enable *Differential Analysis* as well as the analyses it provides.

- Chapter 5 builds an analysis methodology in which tools of different natures are put together, with DECAN as a central tool for coordination.

- In Chapter 6 we present some of the technical challenges a tool such as DECAN raises, and discuss how we handled them.

- Chapter 7 addresses measurement precision, stability and probes instrusiveness. It starts with an analysis and a classification of the most commonly monitored events and proposes an overhead reduction technique for the targeted events.

- Future work suggested and motivated by our research is outlined in Chapter 7 and finally, Chapter 8 presents our conclusions.

## Background on Micro-Processor Architecture

Processor design has seen major developments in recent years. The focus on unicore processors favored the development of complex and powerful designs as well as performant memory hierarchies. A sustained increase in processing speed could be achieved by shrinking transistor size, but problems such as die heat rose, which made further shrinking too costly, Therefore, the design trend shifted toward multicore designs in order to achieve the desired performance needs. In addition to unicore mechanisms, Multi-cores add another level of complexity due to inter-core parallelism. Furthermore, processors need to access the data stored in a central memory outside the processor die. This task is critical and has been of primary concern in processor designs too. It leads to the development of smaller memories close to the processor called caches.

The present chapter reviews some important processor micro-architectural details including those of the Intel Sandy-Bridge platform as it is the main architecture on which we tested and validated our work.

We however note that the notions introduced within the chapter are by far not exhaustive, and that specialized books [49] provide richer and more complete material.

### 2.1 Uni-core Design details

A Uni-core processor is based on a computer architecture that has a single processing unit. In this design, a program counter sequences the work by executing instructions one-by-one. The current instruction has to be finished before the next one starts. This ensures a sequential execution of programs. Program data are stored in an external central memory, and circulate between it and the processor through a bus.

Several improvements were set up to tune the base design in order to achieve better performance. The exploitation of different forms of parallelism allowed to increase instructions throughput. Fast access to data being critical to performance, the addition of several levels of caches shortened the time to access data. In the current section we review some of the most significant improvements.

#### 2.1.1 Pipeline

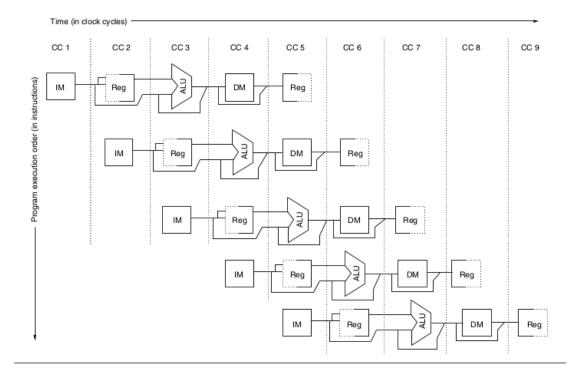

Pipelining is an implementation technique which consists of dividing the instructions execution process into several stages. It allows several instructions to be executed at the same time. This is achieved by leting each isntruction to be in a different stage of the pipeline at a given clock cycle. The technique takes advantage of the opportunity of executing in parallel various actions within an instruction. Pipelining offers the advantage of keeping all portions of the processor occupied. By increasing the amount of useful work done, it increases the throughput of instructions.

Figure 2.1 shows a 5 stages pipeline of a MIPS processor which uses a RISC instruction set [49]. In this architecture, an instruction passes through the following stages to complete execution:

- Instruction Fetch (IF): the next instruction to execute is fetched from memory

- Instruction Decode (ID): decodes the fetched instruction. The decoding recognizes the opcode as well as the operands the instruction uses.

- Execution (EX): Executes the instruction. The execution is handled by the ALU (arithmetic and logic unit), if the opcode corresponds to a memory operation than the effective address is computed, otherwise, the operation is performed on the decoded operands

- Memory Access (MEM): if the operation is a load, the operand is read from memory, an if it is a store, the content of the register operand is written to memory

- Write-back (WB): if the operation produces results, these are written back to the register file.

Figure 2.1: Five stages pipeline [49]

The above pipeline example remains simple compared to modern pipelines. These have more execution stages, some of which can be complex, hence having a latency of more than one cycle. The Sandy-Bridge presented in Section 2.4 gives an overview of such pipelines.

But pipelining generally presents disadvantages too, the most notable being [80]:

• Increased hardware complexity which generates resource conflicts, control dependency and data dependency.

• Pipeline stalls: due to what is called pipeline hazards (data hazards, disrupted control, etc). They prevent smooth execution of the pipeline by causing flows (bubbles) in it.

#### 2.1.2 Multiple Issue Processors

Multiple issue processors (also called Superscalar architectures) are architectures where multiple instructions are issued at the same time. The goal is to achieve a bigger instructions per cycle (IPC) ratio by exploiting the independence available between instructions, introducing what is called instruction level parallelism. In general, multiple issuing is combined with pipelining in order to enable several instructions to be simultaneously initiated within a pipeline stage, in other words a superscalar architecture can be seen as several pipelines working at the same time. The same concept is applied at the pipeline stage level also (e.g. multiple functional units), allowing several operations of the same type to BE executed in parallel. Several types of superscalar architectures have been desgned. We find: statically scheduled superscalar architecture, VLIW (Very Long Instruction Word) and dynamically scheduled superscalar architecture. The later one is the most widespread in current processor designs, it is also the one we focus on within our study.

Superscalar architectures suffer from the same issues as pipelines, namely: resource conflicts, control dependency and data dependency.

#### 2.1.3 Vector Extensions

Vector extensions are parts of the functional units of the processor which work on packed data. A subset of the *Instruction set architecture (ISA)* allows to exploit these units. By doing so, the processor has the ability to exploit data parallelism when possible. In order to expose such parallelism to the processor, the compiler constructs *vectorized loops*. When the vectorization is total, all loads, stores and ALU instructions operate on vectors of data, whereas when it is partial only part of of the instructions operate on vectors of data.

| Vector technology | Assembly instructions   |

|-------------------|-------------------------|

| SSE               | ADDPS XMM1, XMM2        |

| AVX               | VADDPS YMM1, YMM2, YMM3 |

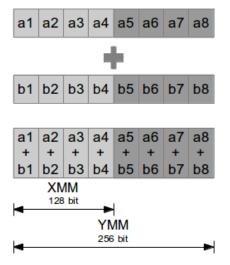

**Figure 2.2:** Vector operations on Intel architectures. The two technologies illustrated are SSE(Streaming SIMD Extensions) and Advanced Vector Extensions (AVX)

Figure 2.2 illustrates an addition operation performed using two technologies of vector extensions implemented in the Intel x86 micro-architecture: 1) Streaming SIMD Extensions (SSE) which works on 128 bit long vectors and is able to pack four elements in single precision (32 bit each) or two elements in double precision (64 bit each), and 2) Advanced Vector Extensions (AVX) which is the successor of SSE on newer Intel micro-architectures. and operates on arrays with double the size of those of the former technology, hence allowing up to eight elements in single precision and four in double precision.

Vector extensions technology is present in other architectures under other names. AMD uses both SSE and AVX in addition to its own technology 3D Now [1], whereas ARM developed its own technology called NEON[5].

#### 2.1.4 Out-Of-Order Execution

Out-Of-Order execution is a technology which enables instructions to not follow the first in first out (FIFO) strategy. Instead, they are buffurized in what is called an instruction window. Within this window, each instruction whith ready operands is dispatched to free functional units. Hence, non-ready instructions cannot block the ready instructions that arrive after them. Once the execution finishes, the processor ensures an in-order commit (WB) of instructions in order to preserve the correct program semantic. In general, out of order execution starts in the execution  $stage\ (EX)$  of the pipeline (see Figure 2.1). The following elements play a key role in an out-of-order engine:

Instruction buffer: when an instruction terminates its passage in a pipeline stage, it is recorded in a temporary register called a latche. Latches enable instruction preservation in case of pipeline stalls. In an in-order pipeline one latche is needed in each stage because only one instruction can be active. In an out-of-order context however, several instructions might be active within a single stage (e.g. EX stage). Therefore, a buffer of instructions at the entry of the Out-of-order area substitutes the latche. The buffer may have different designations but its functionality is the same: providing an area where parallel polling of instructions is possible.

Register renaming: one of the big issues of OOO execution is the handling of data dependencies. Of the three possible data dependencies (WAW, WAR and RAW), only Reads after Writes (RAW) are true dependencies, WAW (writes after writes) and WAR (writes after reads) are possible because the same register name refers to totally independent values. This is due to the fact that there are not enough register IDs in the ISA. Register Renaming is a mechanism that allows to rename register IDs in order to eliminate WAW and WAR dependencies. The renaming mechanism has been first described by Tomasulo in [91], and most modern processors use a variant of that process.

**Speculation**: conditional branch instructions are problematic for the out-oforder engine and the pipeline in general. Until the instruction itself is executed, the next path is not known, therefore it is not possible to know what instructions should enter the pipeline next. In such situations, either no instruction coming after a branch instruction is executed and even prefetched until the outcome of the branch is known, or the processor speculates that one of the two paths will be taken and acts as if it was really the case. The branch prediction mechanism, called branch predictor, helps the prefetcher to determine which instruction stream should be fetched next. However, in the case of a bad prediction (also called mis-prediction), the execution of all instructions which arrived after the branch is invalidated, the pipeline is flushed and execution resumes from the right path. Although instructions executed speculatively are not committed until the outcome of the branch instruction is determined, otherwise, it would not be possible to cancel their effects.

The out-of-order engine introduces issues also. Most notably, if the instruction window (which is a buffer) is full, it becomes impossible to execute new instructions until new slots are free. In the case of long dependency chains between instructions, with costly memory accesses, the waiting time to enter the window can be considerable for the newly decoded instructions.

#### 2.1.5 Caches

As processors evolved and benefited from smaller circuitry, their working frequency has grown faster than the frequency with which memory circuitry operates. Indeed, the two being on different chips, processor technology grew faster than memory technology. As a result, the main memory data access latency became relatively bigger with each technology jump. This problem is commonly known as the *memory wall*[100].

In order to decrease this performance gap, small and fast memories known as caches were introduced. These are located between the processor and the main memory, they can be organized in several levels and have different possible internal organizations and characteristics.

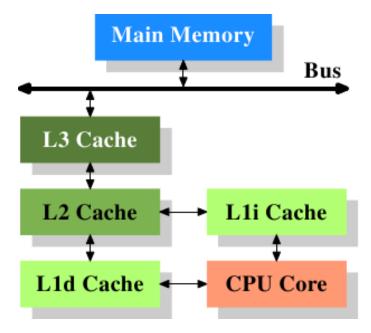

#### 2.1.5.1 Cache Hierarchies

Several levels of cache can be placed between the processor core and the main memory, caches close to the processor core are faster and smaller, those which are far are bigger and slower. Furthermore, a cache can be either *split* or *unified*. In a split cache, instructions are held in an *instructions cache*(I-cache) and data in a data cache(D-cache). On the other hand, a unified cache holds both instructions and data.

A data request from the core is first passed to the L1 cache (the closest to the core). If the data is found there, it is called a *cache hit*, if not, it is called a *cache miss*. In the later case, the request is passed to the L2 cache, if it is found their, then data are passed to the L1, otherwise the request is passed to the L3 cache, the process is repeated until the data are found in a lower cache level, or the request reaches the main memory, and the data is transferred from there to the L2 and L1 caches. Figure 2.3 illustrates this system.

#### 2.1.5.2 Cache characteristics

We enumerate five questions which drive cache caracteristics:

1. Where to put data within the cache: we identify two extreme positions, either the data have only one location in the entire cache, or any location can be

Figure 2.3: Processor with level three cache[13]

used. The former solution is known as *direct mapped* caches, and the second as *fully associative* caches. A third category, known as *set-associative* caches, is a trade-off between the two, and allows a number of caches lines to be placed in one location.

- 2. What to do when the cache is full: when the cache is full and new data need to be placed in it, then an already existing cache line should be evicted. Several eviction techniques are possible: least recently used (LRU), most recently used (MRU), random replacement (RR), etc.

- 3. How to identify data within the cache: only part of the address of data is needed for its placement in cache, therefore, the rest of the address is recorded in a tag register tied to the cache line. More over, mechanisms to verify the validity of data within the cache lines are also needed.

- 4. How to manage a case of write: unlike a read which requires just to find and bring data, a write includes not only findind data but propagates its new value within the entire memory hierarchy. We enumerate two known write strategies: write-back and write-through.

- 5. How to prefetch data chunks: includes all the matters of predicting data that is likely to be used: how much to bring, to which cache level data should be prefetched, how many parallel prefetch streams are needed.

#### 2.1.5.3 Data locality

Caches greatly enhance data access latencies. However, as any sophisticated hardware wiring, they constitute a limited resource, which puts more pressure on the software part in order to exploit them efficiently. We identify two important properties the software needs to take into account:

• temporal locality: a referenced memory location is likely to be referenced again in the near future.

• spacial locality: if a memory location is referenced then it is likely that a nearby location will be referenced in the near future.

#### 2.2 Multi-core Designs

Moore's law, a prediction dating from early 80's and stating that processor speed would double each 1.5 years was no more verified in early 2000. Processor performance increases have begun to slow down. Chip performance attained a 60 % increase per year in the 1990s but decreased to 40 % per year from 2000 to 2004, We could build a slightly faster chip, but it would cost twice the die area while gaining only a 20 percent speed increase, noted Marc Tremblay, chief architect for Sun Microsystems Scalable Systems Group. The performance increase was sustained because of the possibility to make smaller transistors, however, transistors cannot shrink forever. Even now, as transistor components grow thinner, chip manufacturers have struggled to cap power usage and heat generation, two critical problems. As a result, chip manufacturers started to build chips with multiple cores, less powerful but cooler.

Intrinsically, this added many design parameters: number of cores, symmetricity of the cores, memory organization, core interconnects and power management. Moreover, some software programs needed to be rewritten in order to take advantage of the parallelism offered by multiple processing units, raising new questions: what programming paradigm should be used, and how to transform the initial sequential algorithms into parallel algorithms, which are able to utilize efficiently the multiple processing units.

The existence of multiple cores on a single die introduces new challenges related to internal communications and common resource sharing. First, cores should be able to talk or notify each other, hence some sort of a network should be established between them. Second, in contrast with uni-cores, the external main memory is now shared between cores, which means that memory access management has to be more elaborate. Third, if two or more cores run the same program, they would share the same memory space, moreover, they are likely to access the same memory cases, which would be in their local caches. Therefore, in order to maintain a global coherent state of the memory some advanced memory coherency mechanisms are needed.

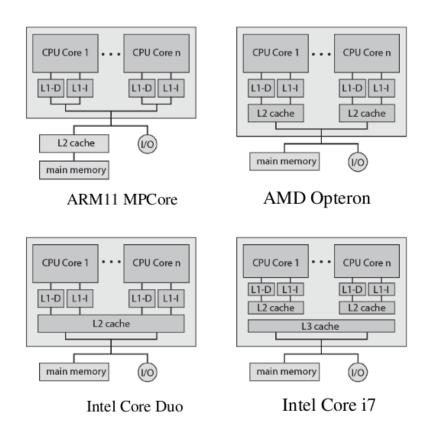

#### 2.2.1 Multiple Cores[92]

A multi-core processor can either integrate similar cores (homogeneous), or cores with differen characteristics (heterogeneous). Most mainstream processors are homogeneous, examples include: Intel and AMD processors. Heterogeneous processors, have at least two cores with differences (e.g. ISA, functionalities, performance). IBM's Cell [54] is probably the most known example of it. In general, both organizations contain pipelined, superscalar cores with vector extensions, for a better exploitation of the ILP. Nonetheless, since in some cases it is hard to exploit such parallelism due to dependences, one can argue in the favor of structures with an increased number of less powerful cores, or else in the exploitation of what is called Simulataneous Multithreading (SMT), which consists of running multiple threads on the same core at the same time.

More over, recent advances in power management make it possible to control

the frequency of each core independently. The control over core frequency change enables the user/OS to define custom power consumption policies for the programs

#### 2.2.2 Cache Organization[21]