# Code optimization based on source to source transformations using profile guided metrics

Thèse de doctorat de l'Université Paris-Saclay préparée à l'Université de Versailles-Saint-Quentin-en-Yvelines

Ecole doctorale n°580 Sciences et technologies de l'information et de la communication (STIC)

Spécialité de doctorat: "Programmation : modèles, algorithmes, langages, architecture"

Thèse présentée et soutenue à Versailles, le 3 Juillet 2019, par

#### YOUENN LEBRAS

#### Composition du Jury:

Anthony Scemama

IR CNRS, HdR, Université de Toulouse Rapporteur

Angelo Steffenel)

McF HdR, Université de Reims Champagne-Ardenne Rapporteur

Michel Masella

CEA DRF, HdR, Saclay Examinateur

Denis Barthou

PR. Université de Bordeaux Président

Sophie Robert

McF, Université d'Orleans Examinateur

William Jalby

PR, Univesité de Versailles Saint-Quentin Directeur de thèse

Andres S. Charif-Rubial

PhD., PeXL Co-encadrant

Romain Dolbeau

PhD ATOS BULL Invité

# Declaration of Authorship

- I, Youenn LEBRAS, declare that this thesis titled, "Code optimization based on source to source transformations using profile guided metrics" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the

exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

| Signed: Youenn LEBRAS |  |

|-----------------------|--|

| Date: 07/03/2019      |  |

#### UVSQ

## Abstract

Paris-Saclay UVSQ - Li-Parad

PhD. Student in Computer Science

Code optimization based on source to source transformations using profile guided metrics by Youenn Lebras

Modern high performance processor architectures tackle performance issues by heavily relying on increased vector lengths and advanced memory hierarchies to deliver high performance. Manual optimization of production HPC codes became a difficult task when having to manage multiple architecture dependent transformations. Developers usually trust compilers to automatically address these performance issues, but they deploy static performance models and heuristics which, must remain conservative or even fail in the worst case. Compiler optimization choices can be refines by using feedback data from dynamic profiling. But, it does not always consider some metrics and is rarely aggressive enough regarding metric data collection. On the other hand, performance analysis tools are pretty good at detecting specific performance issues, but only return observations on the quality and on the execution of the code. Our goal is to develop a framework will allow to perform of source code transformations based on performance analysis tools metrics. This framework will be integrated into the MAQAO tool suite. We present an FDO tool with a set of source-to-source transformations guided by metrics coming from the various MAQAO tools and open to user advices. This framework can also be used to simplify the development by automatically performing some simple, but time-consuming and error-prone transformations (e.g. loop/function specialization).

# Acknowledgements

Avant toute chose, je voudrais remercier M. William Jalby, pour m'avoir acceuilli au sein du laboratoire et pour m'avoir suivi, orienté et soutenu durant cette thèse. Je voudrais aussi remercier Andrès S. Charif-Rubial pour son encadrement.

Je suis reconnaissant envers mes rapporteurs, Anthony Scemama et Angelo Steffenel pour avoir eu la patience de lire ce manuscrit et m'avoir fait des retours pour l'améliorer et sur mes travaux.

Mes années de thèses n'ont pas été de tout repos, mais grâce aux membres de ce laboratoire, elles m'ont paru plus facile à vivre. C'est pourquoi j'adresse un grand merci chacun d'entre eux, pour m'avoir aidé et soutenu que ce soit au travail ou en dehors via les team building au Montbauront et autres occasions. Cédric, pour avoir le courage d'agréger nos MPR pas toujours palpitant chaque mois, pour les soirées graphes avant les reviews et pour les tournées payées. Emmanuel, pour ces longues discussions durant nos trajets pour Teratec. Hugo, mon coéquipier breton de l'équipe, pour nos discussions au montbauront. Jasper, pour tes médecines douces et techniques de relaxation. Mathieu, pour avoir eu la patience (oui, la patience) de m'avoir eu en voisin de bureau et de m'aider à régler de nombreux problèmes d'interface chaise-clavier (que ce soit avec maqao ou pas) ainsi que pour tes citations toujours très inspirées et ton humour noir. A tous, un grand merci!

Je remercie bien évidemment tous les autres membres du laboratoire avec qui j'ai passé moins de temps, mais avec qui j'ai tout autant apprécié travailler/discuter/etc. Kevin, notre stagiaire qui un jour écrira son rapport ; Pablo pour m'avoir aidé dans de nombreuses démarches et avec qui j'ai apprécié travailler et donner des cours ; Yohan, doctorant et compagnon de galère de thèse (adum et formations), Nathalie et sylvain sans qui mon parcours n'aurait peut-être pas été le même, Clément, Marie, Sebastien, pour les différentes discussions et moments qui ont fait que ces années de thèse sont passées si vite.

Evidemment, merci à mes parents et ma soeur, pour leur soutien et pour leur patience lorsqu'ils tentaient de comprendre quel était exactement mon sujet de thèse et en quoi consistait mes travaux.

Un merci plus personnel et tout particulier à Chloé qui m'a soutenue autant (et aussi longtemps) que possible durant cette thèse et ce malgré ce qu'elle vivait. J'espère t'avoir autant soutenu et rendu le bonheur que tu as pu m'apporter. Pour tout ça, je lui dédicace cette thèse.

Un autre remerciement personnel, à mes amis qui sont là pour moi depuis de nombreuses années, Romain et MP, Julien, Jaunathan, Gaetan et Pierre (surtout pour les bières après le travail), Xavier, Jeremy, Zac, Anthony, Cassandre, etc. Il me faudrait encore quelques pages pour citer tout le monde donc je m'arrête là, mais vous pouvez toujours mettre votre nom dans la partie laissée en blanc qui suit.

Merci,

!

And finally, after all these thanks, I would like to thank you random citizen! Yes you, who gonna read this thesis (or at least a brief part). Thank you for thinking that there is something interesting in this manuscript.

## **Contents**

| D | eclara | tion of A | Authorship                               | iii |

|---|--------|-----------|------------------------------------------|-----|

| A | bstrac | et        |                                          | V   |

| A | cknow  | ledgeme:  | nts                                      | vii |

| 1 | Bacl   | kground   |                                          | 1   |

|   | 1.1    | Evoluti   | on of HPC Processor Architectures        | 1   |

|   |        | 1.1.1     | Uni-core Design Details                  | 2   |

|   |        | 1.1.2     | Memory Technology                        | 5   |

|   | 1.2    | With G    | Freat Evolution Comes Great Difficulties | 8   |

|   |        |           | Vectorization Evolution                  | 8   |

|   |        | 1.2.2     | Memory Organization                      | 10  |

|   | 1.3    |           | ers                                      | 12  |

|   |        | 1.3.1     | Introduction                             | 12  |

|   |        | 1.3.2     | Limitations                              | 13  |

|   | 1.4    | Perform   | nance Analysis Tools                     | 14  |

|   |        | 1.4.1     | Static Analysis                          | 14  |

|   |        |           | Dynamic Analysis                         | 16  |

|   |        |           | Using Sampling                           | 16  |

|   |        |           | Using Tracing                            | 18  |

|   |        | 1.4.3     | Global view using both                   | 19  |

|   | 1.5    | Optimi    | zation Tools & Techniques                | 21  |

|   |        |           | Compiler Optimization Techniques         | 21  |

|   |        |           | Flag Research                            | 22  |

|   |        | 1.5.3     | Profile Guided Optimization (PGO)        | 22  |

|   |        |           | Libraries                                | 23  |

|   |        |           | Directives                               | 24  |

|   |        | 1.5.6     | Domain Specific Language                 | 24  |

|   |        |           | Source-to-Source                         | 25  |

|   |        |           | Auto-tuning                              | 26  |

|   | 1.6 | Conclu   | <u>ısion</u>                                       |

|---|-----|----------|----------------------------------------------------|

| 2 | ASS | IST      | 29                                                 |

|   | 2.1 |          | ${ m round}$                                       |

|   |     | 2.1.1    | Specifications / Context                           |

|   |     | 2.1.2    | Existing Tools for Source-to-Source Transformation |

|   |     |          | Cetus                                              |

|   |     |          | Par4All & PIPS                                     |

|   |     |          | OpenC++                                            |

|   |     |          | DMS Software Re-engineering Toolkit                |

|   |     |          | LLVM (Clang & Flang)                               |

|   |     |          | Scout                                              |

|   |     |          | Orio                                               |

|   |     |          | ROSE                                               |

|   |     |          | Summary                                            |

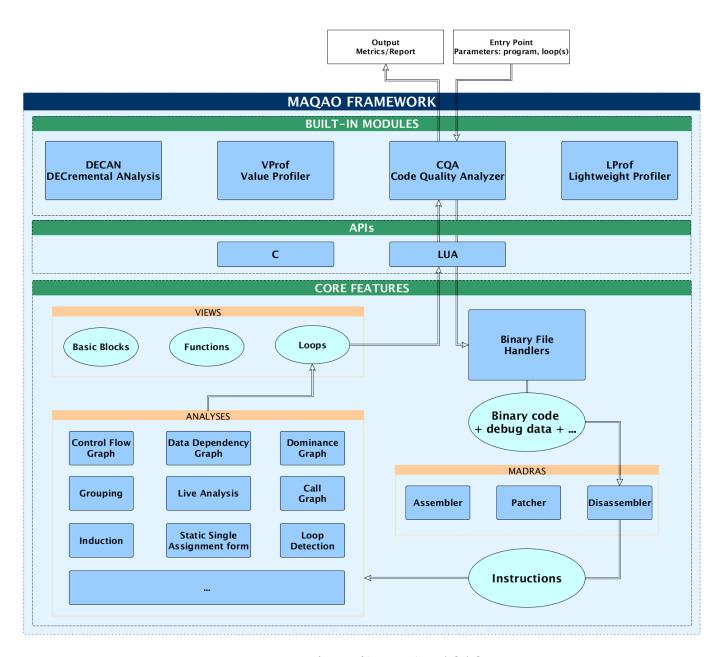

|   |     | 2.1.3    | MAQAO                                              |

|   | 2.2 |          | & Implementation                                   |

|   |     | 2.2.1    | Overview                                           |

|   |     | 2.2.2    | ASSIST Principle                                   |

|   |     | 2.2.3    | Integration Into MAQAO                             |

|   |     | 2.2.4    | Interaction With The User                          |

|   | 2.3 |          | it Supported Transformations                       |

|   |     | 2.3.1    | Unroll                                             |

|   |     | 2.3.2    | Full Unroll                                        |

|   |     | 2.3.3    | Tile                                               |

|   |     | 2.3.4    | Strip Mine         42                              |

|   |     | 2.3.5    | Interchange                                        |

|   |     | 2.3.6    | Loop Count Transformation (LCT)                    |

|   |     | 2.3.7    | Short Vector Transformation (SVT)                  |

|   |     | 2.3.8    | Prefetcher                                         |

|   |     | 2.3.9    | Constant Propagation                               |

|   |     |          | Local Dead Code Elimination                        |

|   |     | 2.3.11   |                                                    |

|   |     |          | Loop                                               |

|   |     |          | Function                                           |

|   | 2.4 | Assess   | ing Transformation Verification                    |

|   |     | 1 2.0000 | How It Works                                       |

|   |     |          | Compared Metrics                                   |

|   |     |          | · · · · · · · · · · · · · · · · · · ·              |

|   |     | Use Case Example                             |

|---|-----|----------------------------------------------|

|   |     | Limitations                                  |

|   | 2.5 | Conclusion                                   |

| 3 | Wha | t Triggers Transformations and How 57        |

| 0 | 3.1 | Introduction                                 |

|   | 3.2 | Collected Data and Triggered Transformations |

|   | J.2 | 3.2.1 Compilers PGOs                         |

|   |     | 3.2.2 AutoFDO                                |

|   | 3.3 | ASSIST Transformations to Trigger            |

|   | 0.0 | 3.3.1 Loop count                             |

|   |     | 3.3.2 Unroll & fullunroll                    |

|   |     | 3.3.3 Interchange                            |

|   |     | 3.3.4 Tile & strip mine                      |

|   |     | 3.3.5 Prefetcher                             |

|   |     | 3.3.6 Specialization                         |

|   |     | 3.3.7 Short vectorization                    |

|   | 3.4 | Conclusion                                   |

| 4 | Evn | eriment 69                                   |

| 4 | 4.1 | Application Pool                             |

|   | 4.1 | Impact of Value Profiling                    |

|   | 4.3 | Impact of Specialization                     |

|   | 4.0 | 4.3.1 Specialization Only                    |

|   |     | 4.3.2 Combined With SVT                      |

|   |     | 4.3.3 Combined With Tiling                   |

|   | 4.4 | Impact of Prefetchers                        |

|   | 1.1 | 4.4.1 With Mini QMCPAK                       |

|   |     | 4.4.2 With AVBP                              |

|   |     | 4.4.3 With Yales2                            |

|   | 4.5 | Impact of Intrinsic Prefetcher Function      |

|   | 1.0 | 4.5.1 With Numerical Recipes                 |

|   |     | 4.5.2 With QMCPACK                           |

|   | 4.6 | Impact of other common transformations       |

|   |     | 4.6.1 With QMCPACK                           |

|   | 4.7 | Conclusion                                   |

|   |     |                                              |

| 5  | Issues & Limitations                               |  | 99  |

|----|----------------------------------------------------|--|-----|

|    | 5.1 Conclusion                                     |  | 103 |

| 6  | Conclusion                                         |  | 105 |

|    | 6.1 Contributions                                  |  | 105 |

|    | 6.2 Perspectives                                   |  | 106 |

| A  | Appendix: ASSIST                                   |  | 111 |

|    | A.1 ASSIST Help                                    |  | 111 |

|    | A.2 ASSIST Comparator Configuration file           |  | 113 |

|    | A.3 Metrics Used for the Comparator                |  | 114 |

|    | A.4 Installation Requirements                      |  | 115 |

|    | A.5 How to Use ASSIST                              |  | 116 |

|    | A.5.1 With an Annotated Source File                |  | 116 |

|    | A.5.2 With Profilers Results                       |  | 116 |

|    | A.5.3 Transformation Script                        |  | 116 |

|    | A.6 Transformation Script                          |  | 117 |

|    | A.7 ASSIST API                                     |  | 118 |

|    | A.8 Example of OneView Report Generated for ASSIST |  | 118 |

|    | A.9 Caveats & Limitations                          |  | 119 |

|    | A.9.1 Preprocessor                                 |  | 119 |

|    | A.9.2 Languages                                    |  | 119 |

| В  | Appendix: Codes                                    |  | 121 |

|    | B.1 Prefetcher                                     |  | 121 |

|    | B.2 Intel Optimization Directives/Pragmas          |  | 123 |

| С  | Appendix: Additional results                       |  | 125 |

|    | C.1 Prefetchers                                    |  | 125 |

| Bi | ibliography                                        |  | 129 |

# **List of Figures**

| 1.1 | DDR1 allows to transfer data on both, the rising and falling edges of the clock                                                                      |                 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|     | signal. Source https://en.wikipedia.org/wiki/Double_data_rate                                                                                        | 7               |

| 1.2 | Sub-part of a cut through a graphics card that uses High Bandwidth Memory.                                                                           |                 |

|     | Grey dots represent: PCI express / Electrical current / Display connectors.                                                                          |                 |

|     | Source: https://en.wikipedia.org/wiki/High_Bandwidth_Memory                                                                                          | 7               |

| 1.3 | Difference of execution between a sequential addition and a vector operation                                                                         |                 |

|     | of addition with vectors of 4 elements. Source: https://www.slideshare.                                                                              |                 |

|     | net/IntelSoftware/the-next-leap-in-javascript-performance                                                                                            | 9               |

| 1.4 | The two possible Intel Optane use cases. Source: Intel(R)-Optane(TM)-                                                                                |                 |

|     | Technology-Workshop-Analyst-and-Press-Slides-322.pdf                                                                                                 | 12              |

| 2.1 | Currency of existing tools performing source to source                                                                                               | 34              |

| 2.1 | Summary of existing tools performing source-to-source                                                                                                | $\frac{34}{35}$ |

|     | •                                                                                                                                                    | 30              |

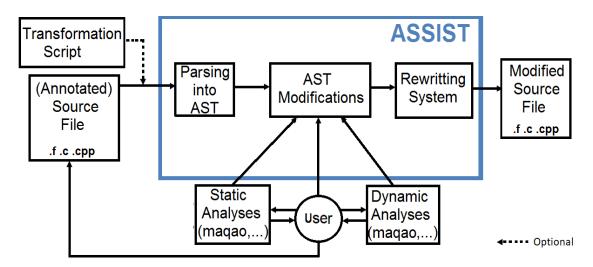

| 2.3 | Overview of tool usage. The user decides what static and dynamic analyses have to be performed. Transformation script is a Lua script where the user |                 |

|     | specifies transformations to be applied, avoiding to directly modify source                                                                          |                 |

|     | code. Alternatively the user can let ASSIST directly use profile to perform                                                                          |                 |

|     | transformations                                                                                                                                      | 37              |

| 2.4 | Example of comparison before and after transformations using ABINIT with                                                                             | 91              |

| 2.1 | the test case Ti-256                                                                                                                                 | 53              |

|     |                                                                                                                                                      |                 |

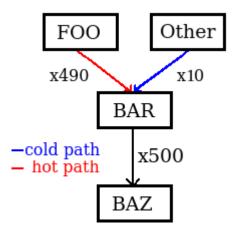

| 3.1 | AutoFDO call graph to detect hot paths throught function calls                                                                                       | 60              |

| 3.2 | Polaris - Metrics global metric before applied the SVT                                                                                               | 65              |

| 3.3 | Polaris - Metrics global and of the two hotspots loops before to apply the SVT.                                                                      | 66              |

| 3.4 | Polaris - Global metrics after the SVT has been applied                                                                                              | 67              |

| 3.5 | Polaris - Global metrics and specific metrics of the two hotspots loops after                                                                        |                 |

|     | the SVT has been applied                                                                                                                             | 67              |

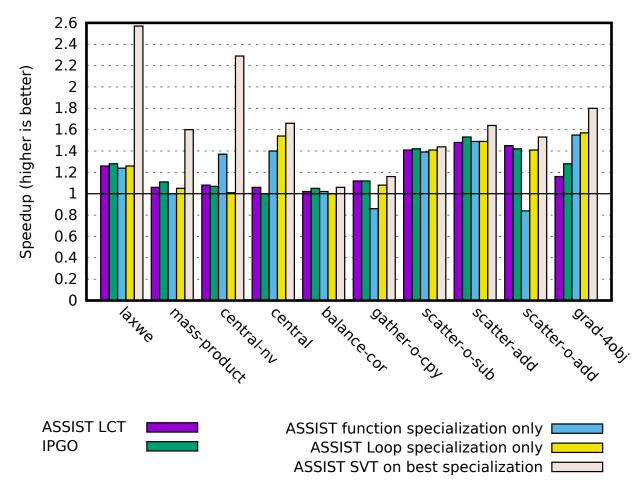

| 4.1  | <b>Histograms</b> : impact (speedup) of ASSIST LCT, IPGO and combination of          |        |

|------|--------------------------------------------------------------------------------------|--------|

|      | both compared with the original version for the same number of threads of            |        |

|      | two datasets Yales2 (Higher is better). <b>Error bars</b> represent original version |        |

|      | divided by minimum speedup and original version divided maximum speedup.             |        |

|      | Plots: Percentage of execution time spent in MPI                                     | 72     |

| 4.2  | Cumulated speedup versus number of loops processed by ASSIST, sorted by              |        |

|      | their coverage, on Yales2 using the 3D CYLINDER test case and AVBP using             |        |

|      | the NASA test case.                                                                  | 74     |

| 4.3  | Convolution Neural Network - Speedup of GoogleNet_V1 layers after special-           |        |

|      | ization, compared to the original version                                            | 75     |

| 4.4  | Speedups by function before and after applying transformations with ASSIST           |        |

|      | (SVT, function/loop specialization, LCT) and IGO compared with the original          |        |

|      | version (higher is better) on AVBP using the SIMPLE test case (sequential            |        |

|      | version)                                                                             | 77     |

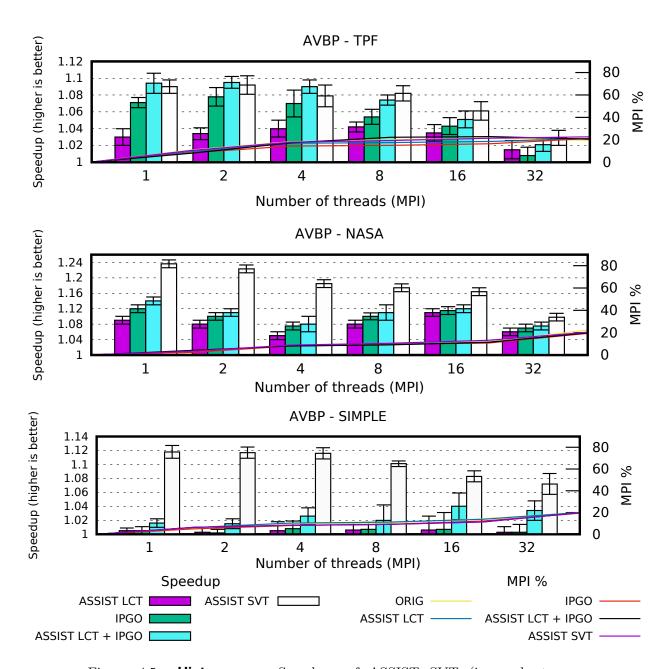

| 4.5  | <b>Histograms</b> : Speedups of ASSIST SVT (i.e. short vectorization+function/loop   |        |

|      | specialization), ASSIST LCT, IPGO and ASSIST LCT+IPGO compared with                  |        |

|      | the original version for the same number of threads (Higher is better) on AVBP       |        |

|      | using NASA, TPF and SIMPLE test cases. <b>Error bars</b> represent original          |        |

|      | version divided by minimum speedup and original version divided maximum              |        |

|      | speedup on AVBP. <b>Plots</b> : Percentage of execution time spent in MPI            | 79     |

| 4.6  | The loop nest of the function "gather_o_cpy"                                         | 81     |

| 4.7  | Original version: Execution time details for the function "gather_o_cpy" and         |        |

|      | all the variants of its loop.                                                        | 81     |

| 4.8  | Function Specialization version: Execution time details for the function "gather_    | o cpy" |

|      | and its loops.                                                                       | 82     |

| 4.9  | Loop Specialization version: Execution time details for the function "gather_o_c     | epy"   |

|      | and its loops.                                                                       | 83     |

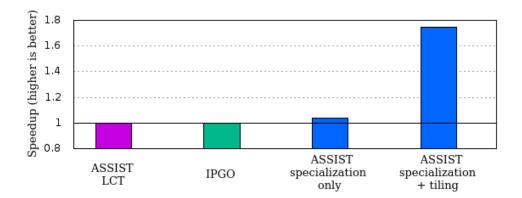

| 4.10 | ABINIT - Example of function specialization coupled with loop tiling, per-           |        |

|      | formed with ASSIST, for the use case Ti-256. Boxes highlight the tiling trans-       |        |

|      | formation of the innermost loop                                                      | 85     |

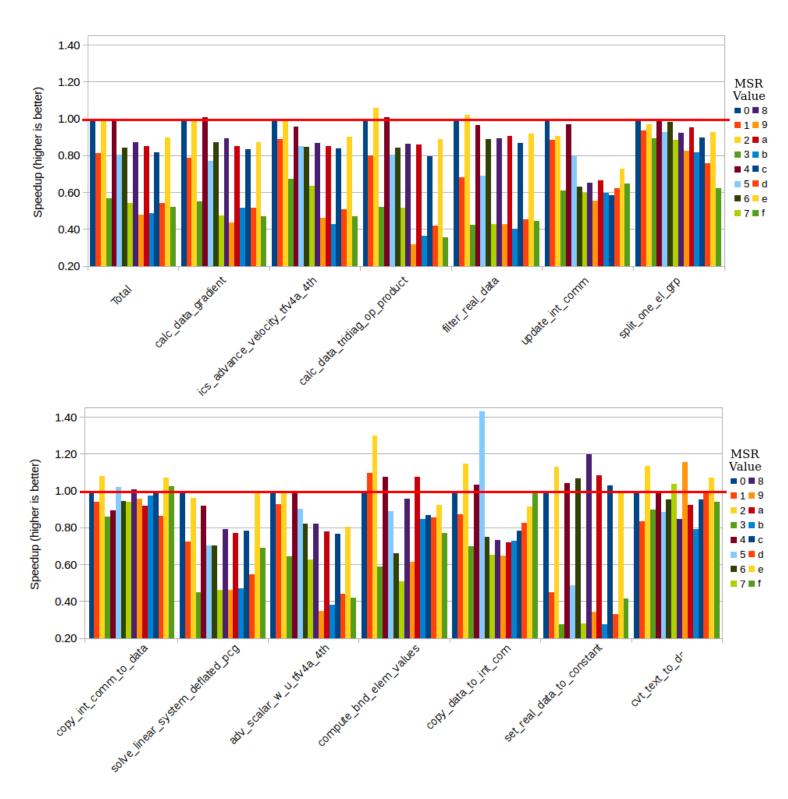

| 4.11 | ABINIT - Ti-256 - Speedups of IPGO, ASSIST LCT, specialized with ASSIST,             |        |

|      | specialized and tiled with ASSIST compared to the original version                   | 86     |

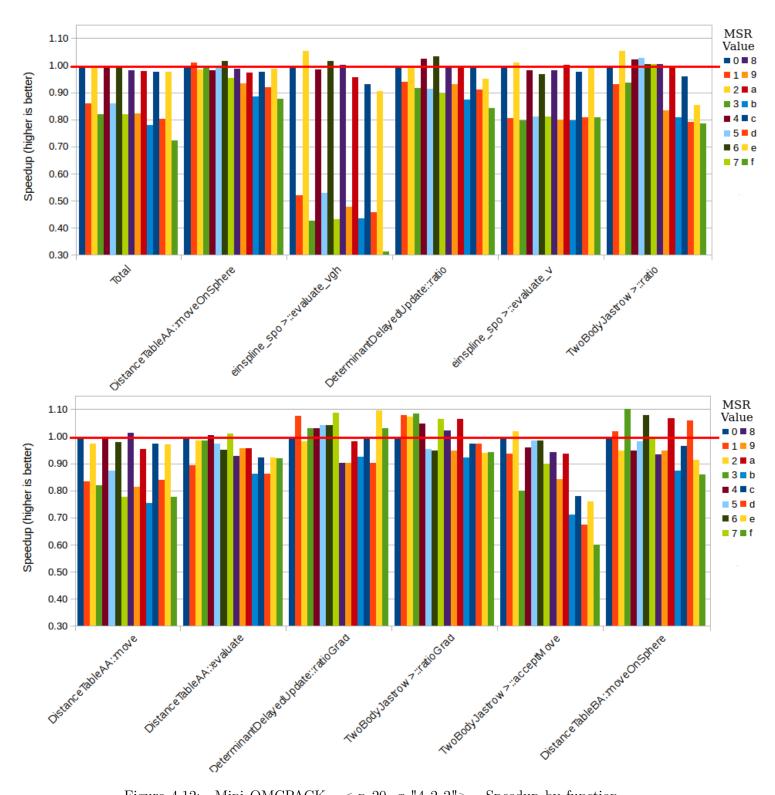

| 4.12 | Mini QMCPACK - <-<br>n 20 -g "4 2 2"> - Speedup by function for all configura-       |        |

|      | tions. All speedups are compared to the configuration 0 (all prefetchers ON).        |        |

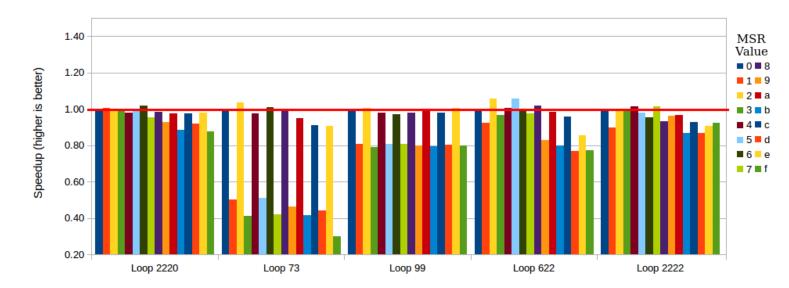

|      | The graph is divided into two parts                                                  | 88     |

| 4.13 | Mini QMCPACK - <-n 20 -g "4 2 2"> - Speedup by loop for all configurations.          |        |

|      | All speedups are compared to the configuration 0 (all prefetchers ON). The           |        |

|      | graph is divided into two parts                                                      | 89     |

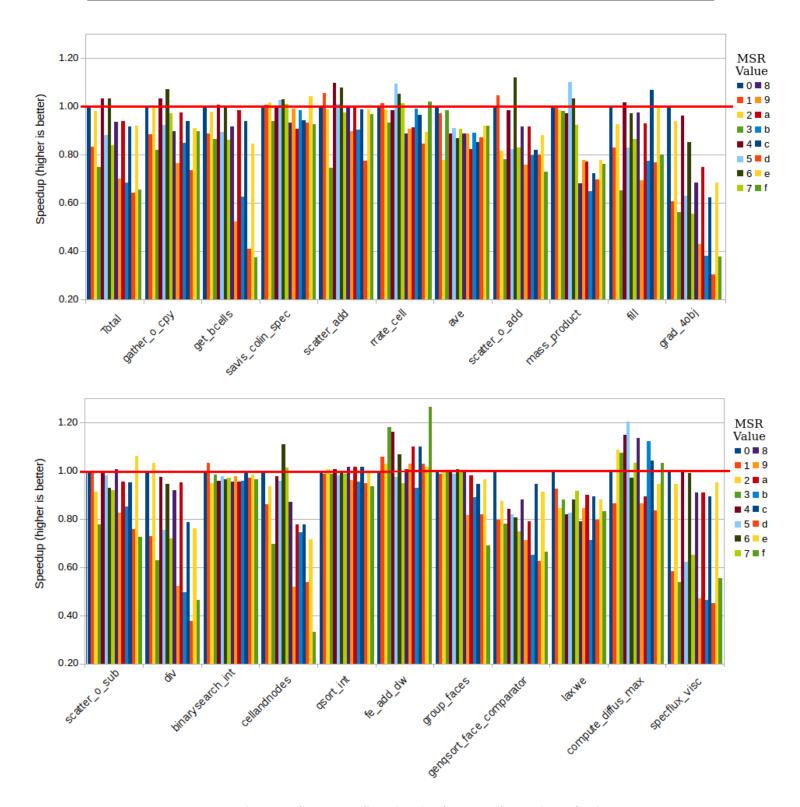

| 4.14 | AVBP - SIMPLE: Speedup by function for each prefetcher configuration. All speedups are compared to the configuration 0 (all prefetchers ON). The graph |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | is divided into two parts.                                                                                                                             | 91  |

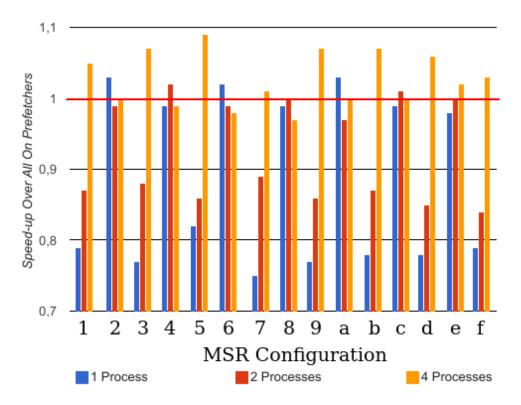

| 4.15 | Yales2- 3D_Cylinder: Speedup by function for each prefetcher combination.                                                                              |     |

|      | All speedups are compared to the configuration 0 (all prefetchers ON). The graph is divided into two parts.                                            | 93  |

| 4.16 | Yales2 - 3D_Cylinder: Speedup by prefetcher combination compared to all prefetchers enabled for one, two and four processes                            | 94  |

| A.1  | Example from POLARIS of Oneview internal report for ASSIST, with on one side global metrics and on the other, the "oneview report" with all metrics    |     |

|      | by loops                                                                                                                                               | 120 |

| C.1  | Oneview view of functions managed                                                                                                                      | 126 |

|      | Speedup by function for each prefetcher behavior.                                                                                                      | 127 |

# **List of Tables**

| 1.1 | Release year, range of number of cores and range of frequencies with and without Turbo Boost for each micro-architecture. Source www.wikipedia.org (only server information has been selected), https://en.wikipedia.org/ |                |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|     | wiki/Transistor_count                                                                                                                                                                                                     | 2              |

| 1.2 | Number of transistors per processor and their area with normalization per 1                                                                                                                                               | 2              |

|     | core. Source https://en.wikipedia.org/wiki/Transistor_count                                                                                                                                                               | 2              |

| 1.3 | Evolution of key parameters on recent architectures. Specialized ports gather:                                                                                                                                            | _              |

|     | AES encryption, vector permutation, SADBW, PCLMUL, jump and branch,                                                                                                                                                       |                |

|     | branch. Source: www.anandtech.com & www.agner.org/optimize/                                                                                                                                                               | 4              |

| 1.4 | Double Data Rate key parameters. "Gigatransfers per second refer to the num-                                                                                                                                              |                |

|     | ber of operations transferring data that occur in each second". Cycle Time                                                                                                                                                |                |

|     | represent time between two clock cycles in nanoseconde. Source: https:                                                                                                                                                    |                |

|     | //en.wikipedia.org/wiki/DDR_SDRAM, https://www.memoireonline.com/                                                                                                                                                         |                |

|     | 01/12/5117/m_volution-sur-la-memoire-vive7.html, https://en.wikiped:                                                                                                                                                      | ia.            |

|     | $\verb org/wiki/Double_data_rate  \&   \verb https://www.transcend-info.com/Support/ $                                                                                                                                    |                |

|     | FAQ-296                                                                                                                                                                                                                   | 6              |

| 1.5 | Evolution of Intel Vector instruction set                                                                                                                                                                                 | 9              |

| 1.6 | Memory hierarchy key parameters L3 latencies fluctuates depending of the                                                                                                                                                  |                |

|     | number of cores, the more L3 slices, the more latency goes up. Cache TLB are                                                                                                                                              | 1, 1           |

|     | presented as follow: "page size: # entries, associativity" Source: https://www.an                                                                                                                                         |                |

|     | and https://en.wikichip.org.                                                                                                                                                                                              | 11             |

| 2.1 | The four types of hardware prefetchers for data prefetching. Source: https://softw                                                                                                                                        | vare.intel.com |

|     |                                                                                                                                                                                                                           | 46             |

| 4.1 | Number of loops processed by ASSIST LCT for each application and test case.                                                                                                                                               | 71             |

| 4.2 | CQA & VPROF metrics of loops of the hotspot functions of AVBP, with the                                                                                                                                                   |                |

|     | SIMPLE dataset, before applying the SVT                                                                                                                                                                                   | 78             |

| 4.3 | Execution time and speedups of ASSIST SVT (i.e. generic short vectorization)                                                                                                                                              |                |

|     | compared with the original version on Polaris using the "test_1.0.5.18" test                                                                                                                                              |                |

|     | 6950                                                                                                                                                                                                                      | 83             |

| 4.4 | $ {\bf The \ different \ prefetcher \ configurations, \ according \ to \ Intel: \ https://software.intel.} $ | com.         |

|-----|--------------------------------------------------------------------------------------------------------------|--------------|

|     | 0=prefetcher ON, 1=prefetcher OFF                                                                            | 87           |

| 4.5 | NR - Number of cycle for the target loop. Prefetch 64, 128, 256, 512 and 1024                                |              |

|     | indicates the distance of the data to prefetch.                                                              | 95           |

| 4.6 | QMCPACK - Number of cycles for the target loop. Prefetch 64, 128, 256, 512                                   |              |

|     | and 1024 indicates the distance of the data to prefetch                                                      | 95           |

| 4.7 | Time in second of multiple versions of QMCPACK. Files have been used as                                      |              |

|     | identifier because they contain multiple loops that have been optimized at the                               |              |

|     | same time. Orig: Original version; FU: Full unroll version; DIV: FU + Divison                                |              |

|     | replaced by multiplications; SIGNBIT: DIV = use signbit function to replace                                  |              |

|     | an if statement; SIMD: SIGNBIT + use of the directive "simd" above signbit                                   |              |

|     | ,                                                                                                            | 06           |

|     | loop                                                                                                         | 96           |

| B.1 | Non-exhaustive list of optimization directives and pragmas available with                                    |              |

|     | the Intel Compiler. Sources: https://software.intel.com/en-us/node/                                          |              |

|     | 524560#EE255A8D-F0AC-4022-A6C0-DA92E6BFC8CE, https://software.intel                                          |              |

|     | com/en-us/fortran-compiler-developer-guide-and-reference-compiler-                                           |              |

|     |                                                                                                              | 101          |

|     |                                                                                                              | 1 <i>2</i> 4 |

## List of Abbreviations

API Application Programming Interface

**AST** Abstract Syntax Tree

AVX Advanced Vector Extensions

DDR Double Data Rate

FDO Feedback Data Optimization

GCC GNU Compiler Collection

GPL General Public License

GWP Google-Wide Profiler

HBM High Bandwidth Memory

**HPC** High Pperformance Computation

IR Intermediate Representation

LCT Loop Count Transformation

LGPL Lesser General Public License

LLVM Low Level Virtual Machine

MAQAO Modular Assembly Quality Analyzer and Optimizer

MSR Model Specific Register

PGO Profile Guided Optimization

RAT Register Aalias Table ROB Re-Ordering Buffer

SIMD Single Instruction on Mmultiple Data

SSE Streaming SIMD Extensions

**SVT** Short Vectorization Transformation

À Chloé.

## Chapter 1

## **Background**

#### 1.1 Evolution of HPC Processor Architectures

This section presents the evolution of High Performance Computing (HPC) processors architecture. To follow this evolution we focus on four micro-architectures of the HPC leader, Intel. In 2007 Intel adopted the "tick-tock" model where a new micro-architecture ("tock") is followed by a die shrink ("tick") and, sometimes, new instructions or features are introduced.

For consistency and stability, this survey only focuses on new micro-architectures designated during the "tock" cycles. First, we present Nehalem, an Intel micro-architecture released in 2008 and successor of the Intel Core 2.

Nehalem-based processors use a 45nm engraving process and allow hyper-threading. This micro-architecture comes with an L2 cache smaller than its predecessors but it embeds a very large L3 cache shared among all cores. The Nehalem "tick" is named Westmere and precedes the Sandy Bridge micro-architecture.

Sandy Bridge, was released in 2011 as the "second-generation core" and was considered as the successor of Nehalem. Sandy Bridge uses a 32nm process and offers a new set of vector instructions (AVX) while retaining most of Nehalem core features. The Sandy Bridge "tick" is named Ivy Bridge and is a 22nm die shrink of the original. The successor of Sandy Bridge is named Haswell.

The Haswell micro-architecture was released in 2013 as the "fourth-generation core", it uses a 22nm process and was specifically designed for power optimization. This micro-architecture was deployed in a wide range of low-power processors for ultrabook computers and saw an upgrade in the vector instruction set (AVX2). Intel also increased the number of some registers and enlarged multiple memory buffer sizes. The "tick" of this micro-architecture is labeled Broadwell and is made using a 14nm process.

Finally, Skylake will be the last micro-architecture we present. It was released in 2015 as the "sixth-generation core" and uses the same 14nm manufacturing process as Broadwell. With Skylake, Intel gave up the "tick-tock" model and offered several alternative versions

| System       | Year | # Cores | Frequency   | Turbo       | Lithography  |

|--------------|------|---------|-------------|-------------|--------------|

|              |      |         | (Ghz)       | (Ghz)       | Process (nm) |

| Nehalem      | 2008 | 1 - 8   | 1.86 - 2.53 | 1.86 - 3.33 | 45           |

| Sandy Bridge | 2011 | 2 - 8   | 1.8 - 3.5   | 1.8 - 4.0   | 32           |

| haswell      | 2013 | 2 - 18  | 1.9 - 4.0   | 2.7 - 4.4   | 22           |

| Skylake      | 2015 | 4 - 56  | 2.0 - 3.6   | 2.3 - 3.8   | 14           |

Table 1.1: Release year, range of number of cores and range of frequencies with and without Turbo Boost for each micro-architecture. Source www.wikipedia.org (only server information has been selected), https://en.wikipedia.org/wiki/Transistor\_count.

| Processor              | #     | Year | Transistor           | Area     | L3 size | Transistor            | Area       | L3 size    |

|------------------------|-------|------|----------------------|----------|---------|-----------------------|------------|------------|

|                        |       |      |                      |          |         | count                 | $(mm^2)$   | (MiB)      |

| Name                   | Cores |      | Count                | $(mm^2)$ | (MiB)   | Normalized            | Normalized | Normalized |

| Xeon Nehalem-EX        | 8     | 2010 | $2.3 \times 10^{9}$  | 684      | 18 - 24 | $0.288 \times 10^{9}$ | 85.5       | 2.25 - 3   |

| Core i7 Sandy Bridge-E | 6     | 2011 | $2.27 \times 10^{9}$ | 434      | 12 - 15 | $0.378 \times 10^{9}$ | 72.33      | 2 - 2.25   |

| Core i7 Haswell-E      | 8     | 2014 | $2.6 \times 10^{9}$  | 355      | 15 - 20 | $0.325 \times 10^{9}$ | 44.5       | 1.9 - 2.5  |

| Core i7 Skylake K      | 4     | 2015 | $1.75 \times 10^{9}$ | 122      | 6 - 15  | $0.437 \times 10^{9}$ | 30.5       | 1.5 - 3.75 |

Table 1.2: Number of transistors per processor and their area with normalization per 1 core. Source https://en.wikipedia.org/wiki/Transistor\_count.

instead: Kaby Lake, Coffee Lake, Cannon Lake and Cascade Lake. Skylake introduces larger vector registers and a new set of vector instructions (AVX512), a deeper out-of-order buffer, more execution units, more load/store bandwidth as well as improvements to Hyper-Threading technology.

The Intel Xeon Phi (MIC: KNF, KNC, KNL) family of processors will not be covered in this work because of its demonstrated low performance, complex requirements and its lack of a developer friendly environment.

## 1.1.1 Uni-core Design Details

Over the last decade, CPU architectures evolved dramatically in terms of performance; from the Pentium family to the last generation of Intel chips (Skylake-X), it is obvious that the

performance model of the market shifted from high frequency single core processors to multitasking high-core-count (or Manycore) parallel architectures. This allowed CPU manufacturers to lower the power consumption (at the cost of latency sometimes) and increase memory bandwidth and instruction throughput. This shift of performance model introduced additional optimization challenges related to parallelism (task and data), compilation and code generation. In such environment, the optimization process is key to maintain a reasonable performance level on modern micro-processor architectures [35]. Jalby et al.[52] presented the progress of performance correlated to the Intel architecture evolution for the last twenty years; and especially how the top 500 most powerful systems struggle to reach peak computational performance on real world applications even with a continuous increase in flops. This evolution brings to light new optimization issues and challenges (i.e. managing larger vector lengths, automatic vectorization, ...) beyond previously encountered performance limiting factors (i.e. pipeline stages, memory hierarchy, ...).

Table 1.1 and 1.2 show the evolution of the technology using the core count, the frequency and the lithography process as performance markers for the presented micro-architectures. CPU performance is not only centered around core count and frequency but can also be affected by the memory hierarchy (cache levels, number of memory channels, ...) and its ability to process instructions and data in fewer cycles, or manipulate more data at once (vectorization). The last two axes are of utmost importance for a micro-architecture to deliver considerable performance. Table 1.3 shows Intel's endeavors to deal with both these axes with micro-architectural upgrades.

"Out-of-Order" execution is an important improvement in micro-architectures design. Basically, on "in-order" processors, if one or more operands are unavailable during the current clock cycle, the processor stalls until they become available. The Out-of-Order process avoids this stall by processing instructions based on their readiness rather than order; each instruction with a ready operand is added into a buffer and dispatched to free units; instruction 2 can be executed before instruction 1 has been completed if all operands to perform instruction 2 are completed. Once the execution finishes, the processor ensures that all instructions are qualified "in-order" to preserve the correct program semantic. This process has been used in microprocessors since 1990; the concept does not change but the size of all buffers or registers has significantly increased, as we can see in table 1.3. The "Out-of-Order" buffer has practically doubled in size from Nehalem to Skylake. The same evolution applies to Stores, Loads and the scheduler entries. The largest increase was for the number of instructions decoding queue which triples with Skylake. The number of execution ports has not increased a lot but ports are now allowed to perform more different kinds of operations; from Haswell, Intel added specialized ports which allow Fused-Multiply-Add (FMA) instructions, Advanced Encryption Standard, Carry-Less Multiplication, ... to be performed.

|                          | Nehalem    | Sandy Bridge | Haswell    | Skylake    |

|--------------------------|------------|--------------|------------|------------|

| Out-of-Order buffer      | 128        | 168          | 192        | 224        |

| ROB entries              | 128        | 168          | 192        | 224        |

| In-flight Stores         | 32         | 36           | 42         | 56         |

| In-flight Loads          | 48         | 64           | 72         | 72         |

| Scheduler Entries        | 36         | 54           | 60         | 97         |

| Integer Register File    | 0          | 144          | 168        | 168        |

| FP Register File         | 0          | 144          | 168        | 168        |

| Line fill buffer         | 10 entries | 10 entries   | 10 entries | 10 entries |

| Instruction Decode Queue | 28/thread  | 28/thread    | 56/thread  | 64/thread  |

| # Execution Ports        | 6          | 6            | 8          | 8          |

| # ALU Ports              | 3          | 3            | 4          | 4          |

| # Read Ports             | 1          | 2            | 2          | 3          |

| # Write Ports            | 1          | 1            | 2          | 2          |

| # Address Calculation    | 1          | 2            | 3          | 3          |

| # FMA Ports              | 0          | 0            | 2          | 3          |

| # Specialized Port       | 0          | 0            | 3          | 4          |

Table 1.3: Evolution of key parameters on recent architectures. Specialized ports gather: AES encryption, vector permutation, SADBW, PCLMUL, jump and branch, branch. Source: www.anandtech.com & www.agner.org/optimize/.

An FMA is a floating-point multiply-add operation performed in one step. "That is, where an unfused multiply-add would compute the product b\*c, round it to N significant bits, add the result to a, and round back to N significant bits, a fused multiply-add would compute the entire expression a + b\*c to its full precision before rounding the final result down to N significant bits". The set of FMA instructions allow faster and more accurate specialized operations and are closely related to vector instruction sets described in the next section.

Modern high-performance processor architectures heavily rely on increased vector lengths and advanced memory hierarchies to deliver high-performance. This stresses the importance of data access optimization and efficient usage of the underlying available vector capabilities detailed in section 1.2.1 and 1.2.2.

#### 1.1.2 Memory Technology

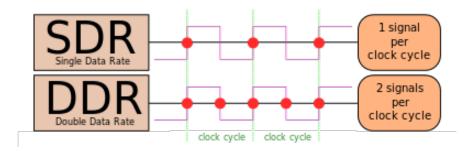

Until recently, the memory was divided into two large families: first, persistent memory (e.g. Hardrive, flash drive); and second, volatile memory (i.e. DRAM, SRAM). For a myriad of reasons, memory technology hasn't evolved as fast and as much as CPU technology. But, the computer bus and interfaces have seen massive improvement in bandwidth and transfer speed over the years. In 2000, the first Double Data Rate (DDR) memory based on the synchronous dynamic random-access memory (SDRAM or DDR1), was released. This technology has better bandwidth transfer rates; the interface allows to transfer data on both the rising and the falling edges of the clock signal and thus doubles the transfer rate. Figure 1.1 presents the evolution of key parameters of the different DDR.

Memory Bus and Interfaces The main factor behind this evolution is bus and interfaces improvement, as we can see on table 1.4 and 1.6. The first DDR was clocked at 100Mhz with an IO bus clock between 100 and 200 Mhz. The DDR2 bus came up even faster and allowed to operate external data twice as fast as its predecessor. All other key parameters have also been improved and even doubled. Prefetcher buffer width moved from 2 bits in DDR1 to 4 bits in DDR2; both the I/O bus clock and the memory clock frequencies were increased to provide a better transfer rate. Compared to DDR2, DDR3 reduces power consumption by 40% by using a lower voltage, 1.5 volts against 1.8 for DDR2 and 2.5 for DDR1. DDR3 introduced features allowing to control the refresh rate according to the Automatic Self Refresh and the Self-Refresh Temperature variation. DDR4, which is supported by Skylake, has a reduced operating voltage of 1.2 volts with an increased transfer rate of 3.2 GT/s. Only

<sup>&</sup>lt;sup>1</sup>Source: https://en.wikipedia.org/wiki/Multiply-accumulate\_operation

|                     | DDR1      | DDR2      | DDR3       | DDR4       |

|---------------------|-----------|-----------|------------|------------|

| Year                | 2000      | 2003      | 2007       | 2014       |

| Memory              | 100       | 200       | 200        | 400        |

| clock (Mhz)         |           |           |            |            |

| I/O bus             | 100 - 200 | 200 - 533 | 400 - 1067 | 800 - 1600 |

| clock (Mhz)         |           |           |            |            |

| Transfer rate       | 0.2       | 0.8       | 1.6        | 3.2        |

| (Gigatransfers/s)   |           |           |            |            |

| Cycle time          | 5 - 6     | 1.8 - 5   | 1.5 - 0.6  | 1.2 - 0.4  |

| (ns)                |           |           |            |            |

| Prefetcher          | 2 bits    | 4 bits    | 8 bits     | 8 bits     |

| buffer width        |           |           |            |            |

| Energy              | 2.5       | 1.8       | 1.5        | 1.2        |

| consumption (Volts) |           |           |            |            |

Table 1.4: Double Data Rate key parameters. "Gigatransfers per second refer to the number of operations transferring data that occur in each second". Cycle Time represent time between two clock cycles in nanoseconde. Source: https://en.wikipedia.org/wiki/DDR\_SDRAM, https://www.memoireonline.com/01/12/5117/m\_volution-sur-la-memoire-vive7.html, https://en.wikipedia.org/wiki/Double\_data\_rate & https://www.transcend-info.com/Support/FAQ-296

Figure 1.1: DDR1 allows to transfer data on both, the rising and falling edges of the clock signal. Source https://en.wikipedia.org/wiki/Double\_data\_rate

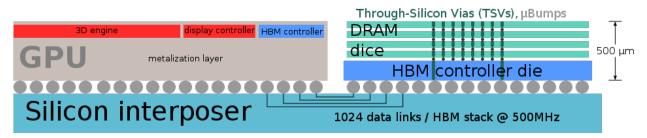

Figure 1.2: Sub-part of a cut through a graphics card that uses High Bandwidth Memory. Grey dots represent: PCI express / Electrical current / Display connectors. Source: https://en.wikipedia.org/wiki/High\_Bandwidth\_Memory

the prefetcher buffer width remained unchanged from DDR3. DDR4 introduces features to improve the stability of data transmission and memory signal integrity. DDR5, planned for 2020, is intended to reduce power consumption while doubling the capacity of the current DDR4.

Other technologies have also been developed; for example, High Bandwidth Memory (HBM), mainly used in GPUs, is designed to stack silicon dies and get a 3D structure for DRAM (2011), as well as a high-performance RAM interface for a 3D-stacked DRAM (2013). Figure 1.2 presents a use of the HBM in a GPU. The HBM memory bus is wider than DRAM bus (i.e. DDR4), it can support up to 4GB per package and has two 128-bits channels per die, for an HBM stack of four DRAM dies, for example. The second generation of HBM, released in 2016, allows up to 8 GB per stack and is able to reach 256 GB/s memory bandwidth per package. A third generation is planned for 2020, and even a fourth between 2022 and 2024, with the objective of reaching the Exascale mark.

Even with improvements to the memory, on Skylake mainly, it remains a complex component with many strong dependencies between caches. Intel has recently introduced the Optane technology, a new class of configurable memory that can function in both, persistent and volatile modes. This adds a new level of complexity above the already complex hierarchy. Intel Optane memory is a smart memory technology that accelerates responsiveness<sup>2</sup> and is named 3D XPoint due to its functioning system; the bit storage is based on a change of bulk resistance, in conjunction with a stackable cross-grided data access array to further boost density<sup>3</sup>. With its new 3D structure with perpendicular wires connecting submicroscopic columns, individual memory cells can be addressed by selecting its top and bottom wire<sup>3</sup>.

#### 1.2 With Great Evolution Comes Great Difficulties

Modern high-performance processor architectures tackle performance issues by heavily relying on increased vector lengths and advanced memory hierarchies in order to deliver high-performance. This stresses the importance of data access optimization and efficient usage of the underlying hardware.

#### 1.2.1 Vectorization Evolution

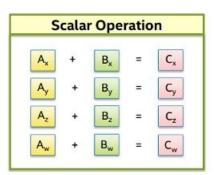

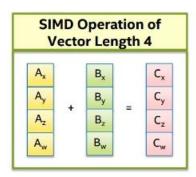

Vector instructions consists of applying the same operation on packed data. Specialized instructions are used for performing vector operations, referred to as SIMD (Single Instruction Multiple Data). Data is loaded in a vector register, and SIMD instructions are used before storing the results in a vector register. In figure 1.3, the scalar operation performs four additions serially, while the SIMD instruction performs only one addition on the four elements.

On Intel microprocessors, the SIMD set of instructions has evolved from what Intel labeled MMX, (extensions to the x86 architecture added in 1996 with Pentium) to AVX-512 (Advanced Vector Extensions), which expands the vector length to 512-bit. AVX-512 was first supported by Intel's Knights Landing processor.

Lately, vectorization has reemerged as a key element for performance. The continuous increase in vector length creates more opportunities to boost the performance of HPC applications. Vectorization is key in the optimization process allowing high-performance and

<sup>&</sup>lt;sup>2</sup>Source: https://www.intel.com/content/www/us/en/architecture-and-technology/optane-memory.html

<sup>&</sup>lt;sup>3</sup>Source: https://www.anandtech.com/

Figure 1.3: Difference of execution between a sequential addition and a vector operation of addition with vectors of 4 elements.

Source: https://www.slideshare.net/IntelSoftware/the-next-leap-in-javascript-performance

| Name   | Vector size | Architecture                      |

|--------|-------------|-----------------------------------|

|        |             |                                   |

| MMX    | 64b         | Pentium 2 (1997)                  |

| SSE    | 128b        | Pentium 3 (1999)                  |

| SSE2   | 128b        | Pentium 4 (2000)                  |

| SSE3   | 128b        | Pentium 4 (2004)                  |

| SSSE3  | 128b        | Merom (2006)                      |

| SSE4.1 | 128b        | Penryn (2007)                     |

| SSE4.2 | 128b        | Nehalem (2008)                    |

| AVX    | 256b        | Sandy Bridge (2011)               |

| AVX2   | 256b        | Haswell (2013)                    |

| AVX512 | 512b        | XeonPhi (2013) & Skylake-X (2017) |

Table 1.5: Evolution of Intel Vector instruction set.

tipping the balance between memory accesses and computation.

However, the advantages are not obvious given that the task of vectorizing and choosing the most appropriate/efficient instructions is left to compilers. Moreover, there's great difficulty in determining whether a loop will be more efficient in sequential or in vectorized form. The compiler uses a static cost model to guide its choice but, without knowledge of loops bounds, it cannot make an optimal choice every time. On Intel architectures, vector instructions are very sensitive to memory alignment and thus exhibit different performances depending on whether allocated memory is aligned to a power of two (or cache line) boundary or not. Although aligned accesses are more efficient, in most cases, it is extremely difficult to generate SIMD code for aligned accesses.

#### 1.2.2 Memory Organization

Memory hierarchy has evolved slowly during the last decade, even after the introduction of the memory wall [121] problem. Table 1.6 presents the evolution of different caches, the translation lookaside buffer (TLB) and latency from Nehalem to latest Skylakes. The low latency values in table 1.6 are explained by the fact that the last level cache is sliced into multiple L3 connected caches. This configuration affects latency but improves the bandwidth. This table shows that the cache and TLB have not evolved much before Skylake which comes with upgraded L2 and L3 caches. With the previous generations of Intel microprocessors, each core had an inclusive private L1 and L2 caches and the last level cache was also inclusive and covered all cores through a bi-directional interconnect. With Skylake-X<sup>TM</sup>, the L3 cache (last level cache) becomes non-inclusive.

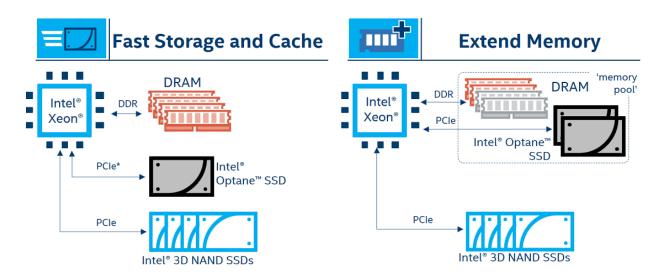

Figure 1.4 presents the two possible use cases of the new Intel Optane technology, which can be used either as a second storage or cache space like an SSD drive, or as extended memory where it will be complementary to the RAM. As shown on figure 1.4 it can be used as complements to the RAM rather than as a complete replacement of it, thus creating a biggest memory pool and a new level in the hierarchy.

Caches Hierarchy As mentioned previously, cache hierarchies have seen little advancements and the improvement of Skylake with larger buffers and increased capacity is not an evolution. However, the new hard drive technology is a revolution in the domain of memory and the Intel Optane technology brings a new approach and is complementary to both RAM and disk level I/O. This technology is too recent and hasn't shown its potential on current HPC workloads. Also, it is unclear what kind of challenges the HPC developers will have to face when this technology becomes more available. What must be kept in mind is that this

|                      | Nehalem              | Sandy Bridge       | Haswell            | Skylake        |

|----------------------|----------------------|--------------------|--------------------|----------------|

| Cache line size      | 64-bytes             | 64-bytes           | 64-bytes           | 64-bytes       |

| L1 Instruction Cache | 32K, 4-way           | 32K, 8-way         | 32K, 8-way         | 32K, 8-way     |

| L1 Data Cache        | 32K, 8-way           | 32K, 8-way         | 32K, 8-way         | 32K, 8-way     |

| L2 Unified Cache     | 256K, 8-way          | 256K, 8-way        | 256K, 8-way        | 1M, 16-way     |

| L3 Data Cache        | 8M,                  | 8M,                | 8M,                | 2M/core,       |

|                      | 16-way               | 12-way             | 12-16 way          | 11-16 way      |

| L1 Instruction       | 4K(page):            | 4K(page):          | 4K(page):          | 4K(page):      |

| TLB                  | 128(entries),4-way   | 128(entries),4-way | 128(entries),4-way | 128(entries),  |

|                      | 2/4M(page): 7/thread | 2/4M: 8/thread     | 2/4M: $8/thread$   | 4-way          |

|                      | 4K(page):            | 4K(page):          | 4K(page)           | 4K(page):      |

| L1 Data              | 64(entries), 4-way   | 64(entries), 4-way | 64(entries), 4-way | 64(entries),   |

| TLB                  | 2/4M(page):          | 2/4M(page):        | 2/4M(page):        | 4-way          |

|                      | 32(entries), 4-way   | 32(entries), 4-way | 32(entries), 4-way |                |

|                      | 1G(page):            | 1G(page):          | 1G(page):          |                |

|                      | fractured            | 4(entries),4-way   | 4(entries),4-way   |                |

| L2 Unified           | 4K(page):            | 4K(page):          | 4K+2M(page)shared: | 4K(page):      |

| TLB                  | 512(entries),        | 512(entries),      | 1024(entries),     | 1536(entries), |

|                      | 4-way                | 4-way              | 8-way              | 12-way         |

| L1 Latency           | 4 cycles             | 4-5 cycles         | 4-5 cycles         | 4-5 cycles     |

| L2 Latency           | 10 cycles            | 11 cycles          | 12 cycles          | 12 cycles      |

| L3 Latency           | depend $\#$ of cores | 30 cycles          | 34-65 cycles       | 34-45 cycles   |

| Line fill buffer     | 10 entries           | 10 entries         | 10 entries         | 10 entries     |

Table 1.6: Memory hierarchy key parameters L3 latencies fluctuates depending of the number of cores, the more L3 slices, the more latency goes up. Cache TLB are presented as follow:

"page size : # entries, associativity"

Source: https://www.anandtech.com and https://en.wikichip.org.

Figure 1.4: The two possible Intel Optane use cases. Source: Intel(R)-Optane(TM)-Technology-Workshop-Analyst-and-Press-Slides-322.pdf

technological breakthrough shows that memory can - indeed - be improved and that it will be a key element in the future when dealing with optimization.

Currently, most memory issues are related to data accesses and alignment, whereas most optimizations focus on how to better manage computation or parallelism, communications and synchronization. With new technologies such as Intel Optane and advancements in bus and other memory interfaces, the paradigm will certainly shift to current memory problems. The future of the evolution will be at the DRAM level with the possibility of the disappearance of hard drives and even SSDs.

## 1.3 Compilers

#### 1.3.1 Introduction

Compilers are the starting point for developers to start optimizing an application. A compiler processes statements written in a human-readable language and turns them into machine language or "code" that a microprocessor chip executes. This process consists of three main steps. First, the frontend, during which the compiler checks the grammar and syntax of the code. Next, the code is transformed into an Abstract Syntax Tree (AST) with an Intermediate Representation (IR) where it applies major optimizations. Finally, the IR is

1.3. Compilers

transformed into assembly code for a target micro-architecture. During the optimization process, every part of the code is statically analyzed and tries to apply as many optimizations as possible. Compilers have a plethora of available optimizations such as loop optimizations (i.e. unroll, split, interchange), vectorization, data-flow optimization (constant propagation, sub-expression elimination, induction variable recognition, and elimination) and code-block reordering. Compilers deploy the latest optimization techniques that offer many benefits to embedded systems developers. With challenging real-time performance goals, cost constraints, developers increasingly rely on the compiler's intimate knowledge of a processor instruction set and performance patterns to produce optimal code.

To help choose which optimizations to apply, static performance models and heuristics are used to avoid degrading the performances. In addition, compilers provide multiple ways to add information to help making choices. For example, developers can give hints about what to expect from some part of their codes by using directives. These hints can be information about the expected trip count for a loop, whether a loop can be vectorized, or even force the vectorization, enable/disable unrolling.

Compilers also provide different flags to trigger optimizations, adding debug information in the binary or control flow. Flags have to be specified during the compilation pass, and can be applied on a unique file or a whole project to maximize their impact. Some compilers also have an integrated Feedback Data Optimization (FDO) tool to help them in their optimization choices, i.e. Profile Guided Optimization (PGO). PGO is a dynamic analysis of a program that runs a dataset to extract specific information and applies other transformations. The three steps of PGO consist of producing an instrumented binary, generating profiling data by running the instrumented binary, and using the collected data to produce a new optimized binary.

However, even with all available optimization possibilities, compilers suffer from limitations where every compiler decision is not obviously optimal. In Chapter 4, we will discuss compiler issues and expected improvements. Usually, due to the cost in time of the research, flag optimizations are applied after the developer has performed source optimizations.

#### 1.3.2 Limitations

Most of the time, developers trust compilers to automatically address performance issues but, sometimes, due to the static performance cost model and heuristics, compilers remain conservative when applying certain optimizations, or fail in the worst case. These static

analyses and strict performance cost models are the main limitation behind compiler optmization failures. Even though developers can provide hints to the compiler using directives, their number is limited and they are compiler dependent. Also, some compiler directives can be hazardous. For example, if a loop is forcefully vectorized, the resulting code can be very slow or worst, and can introduce bugs. The same can be said for flags. Limited in number and scope. In addition, flags are applied on a whole file or project and cannot be applied on a specific part of the code. Another limitation of flags is that they do not always allow performance gain so they have to be used partially and tested carefully. Even if they can be combined, the number of flag combinations which can be applied can increase very quickly. Assuming K compiler flags available, properly setting a string of N flags leads to exploring  $K^N$  combinations [52]. Research about flag combination is expensive because the code must be executed several times to obtain the most optimal combination. The use of the PGO to overcome the issue of the static analysis is limited. PGO lacks information on what is done and in the current implementation, the amount of information gathered at runtime is limited. Moreover, the available transformations space is still fairly small. Both of these limitations have a strong negative impact on the efficiency of the applied transformations. Another limitation is that mapping may miss opportunities for performance enhancements in exchange for correctness or portability.

## 1.4 Performance Analysis Tools

In the HPC industry, optimization is the key to reach peak application performance. Tools, such as profilers and analyzers can be extremely helpful in locating performance bottlenecks and can also help application developers optimize their programs and clear up these performance issues. This section presents different profilers and analyzers which can be classified into two types: static and dynamic.

## 1.4.1 Static Analysis

Static analysis is a method which consists of examining a code without executing it. Static analysis allows an understanding of the code structure and can predict some issues using metrics. The principal advantage of this method is that without executing the program it provides the first estimation of different issues of the code, as well as a code quality control.

**IACA (Intel Architecture Code Analyzer) [48]** is a static analysis tool made by Intel to statically analyze the scheduling of instructions when executed by modern Intel processors. On the one hand, it allows performing static analysis of kernel throughput and latency under

the ideal front-end, Out-of-Order engine and memory hierarchy conditions. On the other hand, it identifies the binding of the kernel instructions to the processor ports and the kernel critical path<sup>4</sup>. IACA enables a first-order estimate of relative kernel performance on different micro-architectures, but does not provide absolute performance numbers.

**Kerncraft [45]** is a tool which analyzes loop kernels using the Execution Cache Memory model, the Roofline model and actual benchmarks. It investigates the data reuse and cache requirements by static code analysis<sup>5</sup>. When combined with Intel IACA, kerncraft can give an overview of both in-core and memory bottlenecks and performance models can be applied on that data.

**Ilvm-mca** [16] is a performance analysis tool that uses information available in LLVM to statically measure the performance of machine code in a specific CPU. Performance is measured in terms of throughput as well as processor resource consumption<sup>6</sup>. It starts by parsing an assembly code, executing a module to simulate the execution of a machine and analyzing the output to generate performance reports. For example, in its report, llvm-mca estimates the Instructions Per Cycle (IPC), as well as hardware resource pressure or provides a timeline view which shows each instruction state transitions through an instruction pipeline. The main goal of this tool is to predict the performance. It also helps with diagnosing potential performance issues. The analysis and reporting were inspired by the IACA tool from Intel.

MIRA [53] is a static analyzer using Rose to perform its analysis of binaries and their associated source code. MIRA generates one AST from the source code and one from the compiled binary code, then tries to match them and uses information retrieved from these trees to improve the accuracy of the generated model. Their analysis focuses on loops and uses the polyhedral model to formalize loops in their general model.

**CQA [23] (Code Quality Analyzer)** is a static analysis module of MAQAO [12] that aims at tackling core level issues by modeling the processor pipeline, performing a simulation of the relevant stages of the hot-spots in a program, and providing numerous metrics that characterize these hot-spots behavior. CQA gathers multiple metrics such as an estimation of data dependencies, vectorization ratio as well as the cycle cost - from the evaluation of

$<sup>^4\</sup>mathrm{Source}$ : https://software.intel.com/en-us/articles/intel-architecture-code-analyzer

<sup>&</sup>lt;sup>5</sup>Source: https://github.com/RRZE-HPC/kerncraft

<sup>&</sup>lt;sup>6</sup>Source: https://llvm.org/docs/CommandGuide/llvm-mca.html

the cost of a group of instructions to know the execution latency and throughput of every instruction variant on a target architecture, execution units and decoding time of instructions.

UFS [85] (Uop Flow Simulation) is an approach combining static analysis and cycle-accurate simulation to very quickly estimate a loop execution time while accounting for out-of-order limitations in modern CPUs. UFS allows to model the impact of varying latency: this can be done uniformly on loads and stores or individually. This allows to understand the potential performance gain of: better blocking (blocking for L2 instead of L3), better prefetching (add extra prefetch instructions on targeted loads), using on-die DRAM versus external DRAM (cf. KNL). In addition, it can correlate code with buffer usage and provide a detailed insight on this buffer usage. UFS allows to characterize the latency impact on loop performance with massive parameter explorations.

## 1.4.2 Dynamic Analysis

In contrast to static analysis which only requires source code and/or binary, dynamic analysis needs to execute the program to gather information. The objective is to find what happened during the execution of a program rather than by repeatedly examining the code offline. The dynamic analysis can be split into sampling and tracing and each has advantages and drawbacks. Both are made to reveal performance issues and to identify which parts of a program the process of improvement will be the most time consuming. Efforts will be focused on investigating and improving them. Sampling is statistical profiling, when the program is repeatedly interrupted as it runs, with a fixed interval between interruptions. The purpose of each interruption is to take a sample. This is done by visiting each running thread, and then examining the stack to discover which functions are running. On the other hand, tracing uses an event logged in the program. This log has to be detailed enough to report execution of function calls, returns, and other statements. Tracing may require the program to be instrumented by inserting instrumentation directly in the source code or dynamically into the machine code.

## **Using Sampling**

Sampling is a statistical profiling process or technique that takes samples. This method does not require any modification of the binary and can use hardware counters to get information about what happens during the execution of the program. Sampling is often sufficient to

$<sup>^{7}</sup> Source: \ https://dyninst.github.io/scalable_tools_workshop/petascale2017/assets/slides/SWT2017_WJA_data_latency_access_V9.pdf$

<sup>&</sup>lt;sup>8</sup>Source: https://www.jwhitham.org/2016/02/profiling-versus-tracing.html

pinpoint load imbalance due to problem decomposition and/or identify the origin of excessive communication time<sup>9</sup>. It is fastest, cheaper than tracing and can be useful as the first step to categorize some issues and to localize performance problems but it can lack accuracy.

**Scalasca [39]** is a software tool that supports the performance optimization of parallel programs by measuring and analyzing their runtime behavior. The analysis identifies potential performance bottlenecks, in particular, those concerning communication and synchronization, and offers guidance in exploring their causes <sup>10</sup>. Scalasca focuses its profiling on parallel issues, such as communications and synchronization inefficiency but nothing on computation issues. The Scalasca analysis can be visualized in other tools, such as cube [29], Paraver [66] or Vampir [112].

**VTune [4]** is a commercial application for software performance analysis of Intel architectures. It provides various kinds of code profiling including stack sampling, thread profiling, and hardware event sampling. The profiler result consists of details such as time spent in each subroutine which can be drilled down to the instruction level. The time taken by the instructions are indicative of any stalls in the pipeline during instruction execution. The tool can also be used to analyze thread and storage performance<sup>11</sup>.

**PerfExpert 4.0 [89, 20]** is a tool that diagnoses performance bottleneck at the function and loop level for any core/socket/node level. It is able to perform source transformation based on specific patterns on identified bottlenecks. PerfExpert also provides an analysis report with hints on how to remove bottlenecks if optimization cannot be done automatically using their source transformation. The report gives an overview of multiple elements of the program. For example, it gives details on the data accesses (hits and misses of all cache levels) and instruction accesses by counting the LPCI arising from accesses to memory: memory accesses for variables, floating point instruction by counting the LPCI from executing floating point instructions, gflops peak. The number of transformations are pattern based and limited to loop interchange, tiling and fission. Moreover, PerfExpert uses HPCToolkit for the analysis and the Rose compiler, for source-to-source, to perform transformations <sup>12</sup>.

<sup>&</sup>lt;sup>9</sup>Source: http://ipm-hpc.sourceforge.net/profilingvstracing.html

<sup>&</sup>lt;sup>10</sup>Source http://www.scalasca.org/

<sup>&</sup>lt;sup>11</sup>Source: https://en.wikipedia.org/wiki/VTune

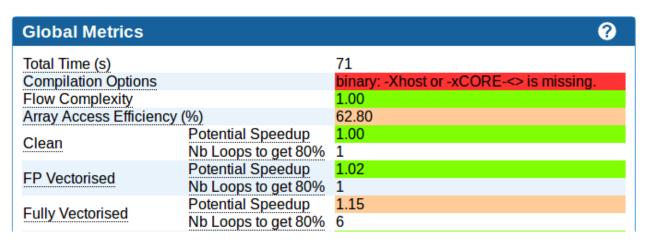

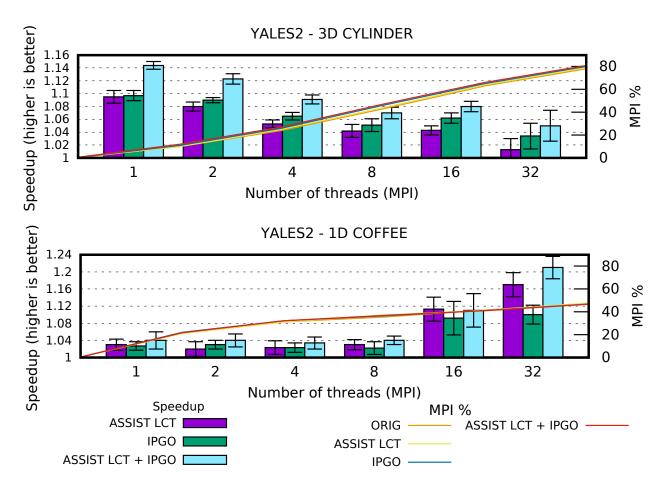

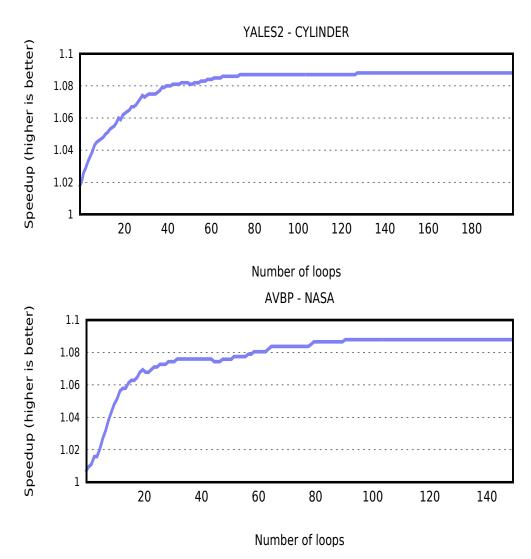

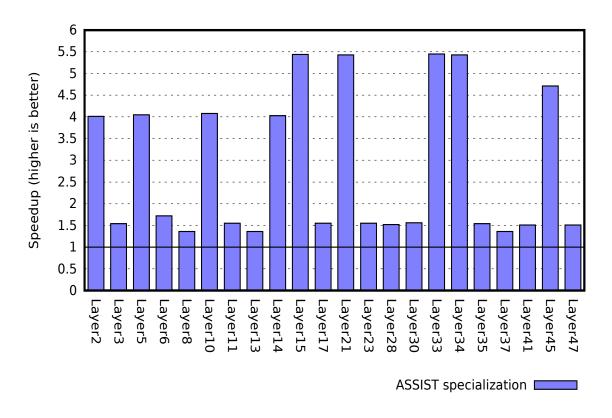

<sup>12</sup>https://github.com/TACC/perfexpert/blob/master/doc/user\_manual/pdf/user\_manual.pdf